写给有经验 PCB 工程师的 Cadence SPB 17.4 极速上手指南

楷登电子 Cadence

推出的 Allegro/OrCAD SPB 是一款专业的板级 EDA

工具,其融合了原理图设计、电路仿真、PCB 绘制编辑、拓扑逻辑自动布线、信号完整性分析、设计输出

等功能,经常被运用于高速 PCB

设计场景。撰写这篇文章的目的,是为已经具备有其它 EDA

使用经验的工程师,快速的上手 Cadence SPB

全家桶设计套件。本文撰写时所采用的是 Cadence SPB 17.4

版本,并且将补丁更新至

Hotfix_SPB17.40.037,该版本的基础操作与快捷键,与目前最新的

23.1

版本基本相同,且两者的工程文件相互兼容,无需进行任何额外的数据转换。全文提供了清晰的目录结构,便于读者按图索骥与查缺补漏。

Cadence SPB SPB 17.4 版本于 2019 年推出,在兼容早期

17.2 和 16.6

版本工程文件的基础之上,还进行了一系列全新的功能升级。其在老版本基础上新增了一套暗黑主题,并且对工具栏的图标以及主界面的窗口进行了重组。最为重要的更新在于支持从原理图直接创建

PCB,且可以方便的实现两者的同步操作。除此之外,还提供了 Web

搜索功能,可以方便的从 Samacsys

和 Ultra

Librarian 下载

原理图符号、PCB 封装、数据手册

以及 3D 模型。

Cadence SPB 安装与启动

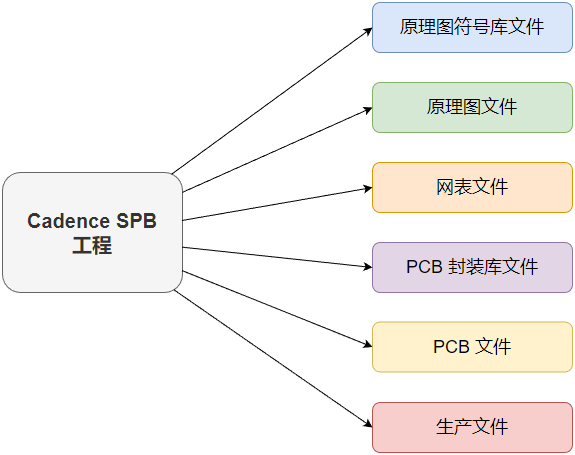

Allegro/OrCAD SPB 17.4 套件当中的 OrCAD

Capture CIS 工具主要用于原理图设计,而 Allegro

PCB 工具则主要用于 PCB 绘制。一个完整的 Cadence

SPB

工程,会同时包含有元件库文件、原理图文件、PCB 库文件、网表文件、PCB 文件、生产文件:

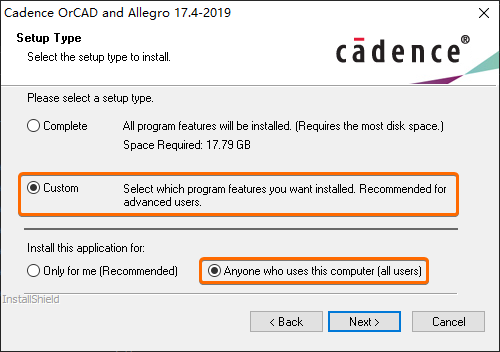

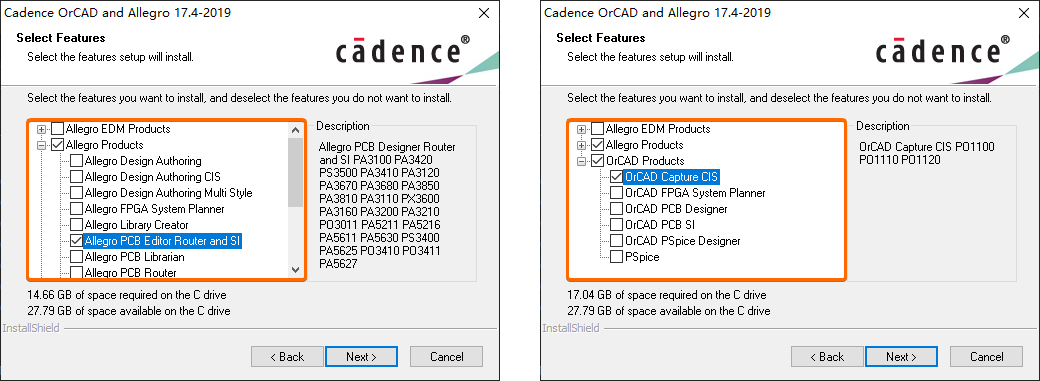

安装 Cadence OrCAD and Allegro 17.4-2019 套件的过程当中,需要勾选安装类型为【Custom】自定义安装,并且勾选为使用该计算机的所有用户安装(可以根据使用环境酌情选择):

在接下来的安装特性选择对话框当中,只需要选择【OrCAD Products】下面的 OrCAD Capture CIS 和【Allegro Products】下面的 Allegro PCB Editor Router and SI 两款工具即可:

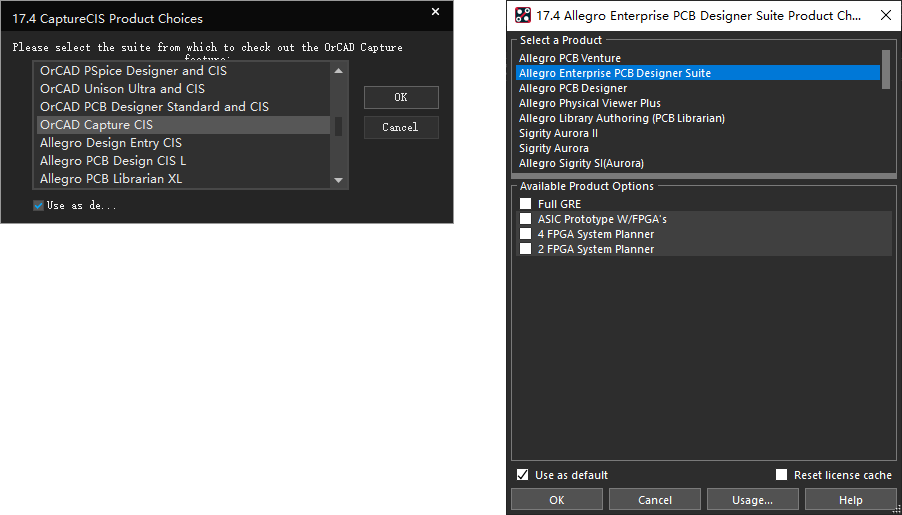

安装完成之后,分别在开始菜单栏输入 Capture CIS 17.4 和

PCB Editor 17.4 就可以打开相应的原理图与 PCB

设计工具。在接下来弹出的产品选择对话框当中,通常会分别选择

OrCAD Capture CIS 作为原理图编辑工具,而

Allegro Enterprise PCB Designer Suite 作为 PCB

绘制工具:

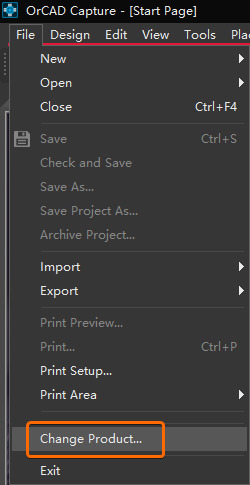

如果需要重新选择原理图编辑器,则可以在没有打开任何原理图工程的情况下,启动

Capture CIS 17.4 之后,鼠标依次选择菜单栏上面的【File ->

Change Product...】项:

下面的表格里,罗列出了一个 Cadence SPB 工程当中,一些经常出现的工程文件后缀名称,便于大家在使用的时候加以区分:

| 文件类型 | 文件后缀 | 文件类型 | 文件后缀 |

|---|---|---|---|

| Cadence SPB 工程文件 | .opj |

Flash 焊盘文件 | .fsm |

| 原理图符号库文件 | .olb |

格式化符号 | .osm |

| 原理图文件 | .dsn |

无电气特性的机械零件 | .bsm |

| PCB 版图文件 | .brd |

可编辑封装文件 | .dra |

| Cadence SPB 网表文件 | .dat |

自定义焊盘图形文件 | .ssm |

| 第三方网表文件 | .net |

操作记录文件 | .jrl |

| PCB 封装文件 | .psm |

处理日志文件 | .log |

| 焊盘文件 | .pad |

新建一个原理图工程

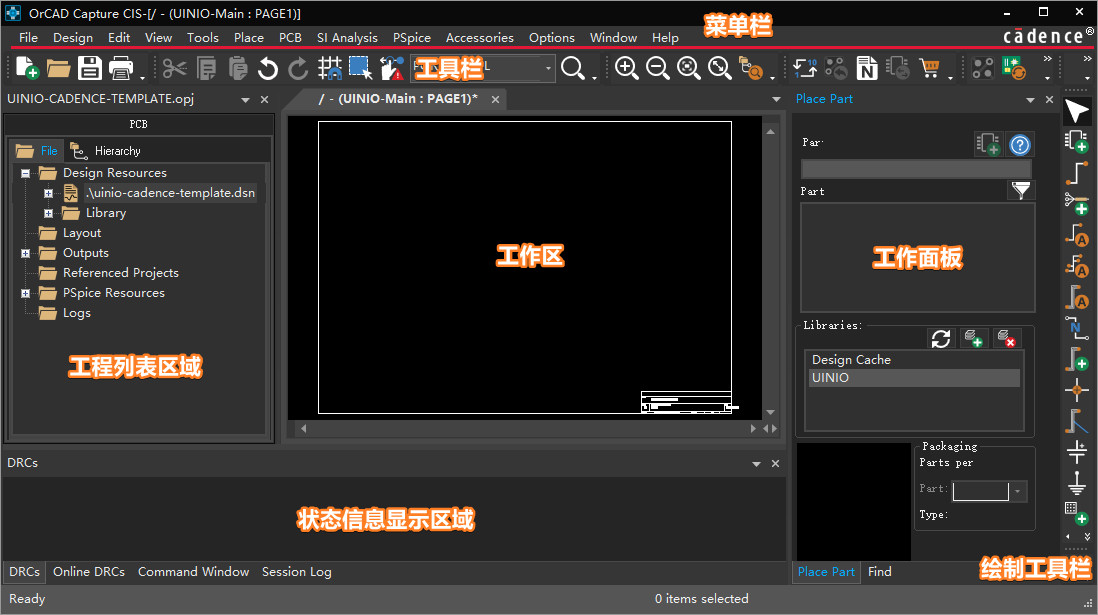

打开 Cadence SPB 套件当中的 OrCAD Capture CIS 之后,呈现出的主界面如下图所示:

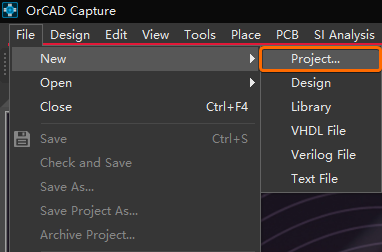

首先,在操作系统的当前工作目录下,手动新建一个

UINIO-Cadence-Template 空文件夹,然后打开 OrCAD

Capture CIS 菜单栏的【File -> New ->

Project...】新建一个工程:

在弹出的对话框当中,分别填写工程的名称,并且指定工程所在的位置,也就是上面新建的

UINIO-Cadence-Template 目录:

这个时候,UINIO-Cadence-Template

目录下的工程文件结构如下所示:

1 | └─UINIO-Cadence-Template |

一些基本的偏好设置

Cadence SPB SPB 17.4

带来的一大变化就是可以支持暗黑界面的显示,鼠标点击 OrCAD Capture

CIS 菜单栏上的【Options -> Preferences】,在弹出的

Preferences 对话框里,修改【Colors/Print】选项卡下的

Application Theme 项为 Dark:

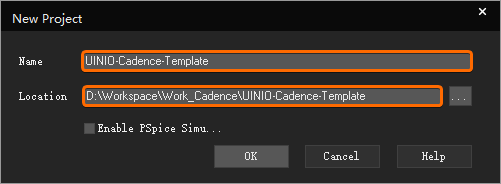

然后,切换至【Grid Display】选项卡,修改工作区的网格风格为线条

Lines:

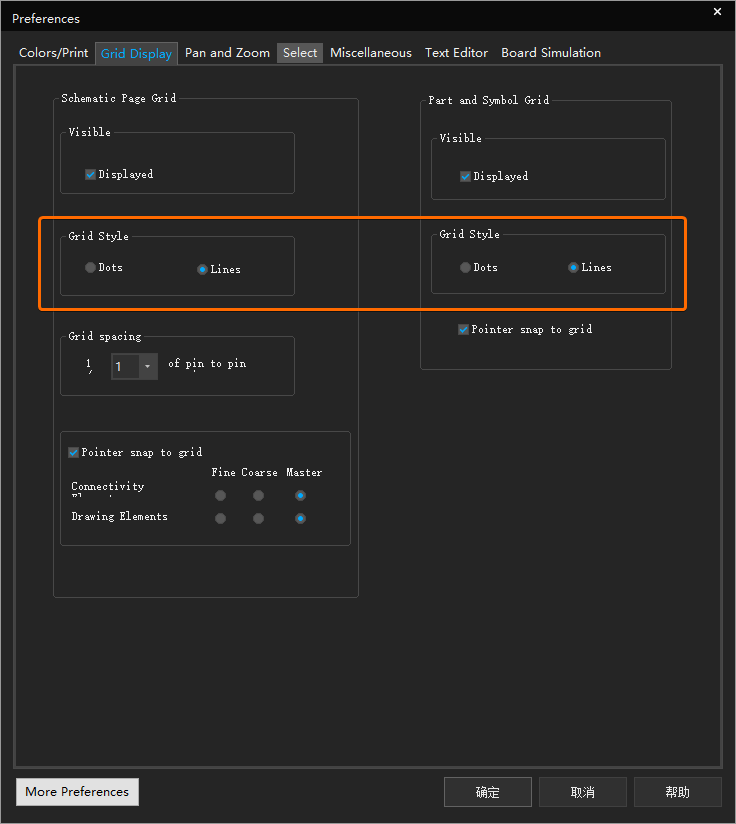

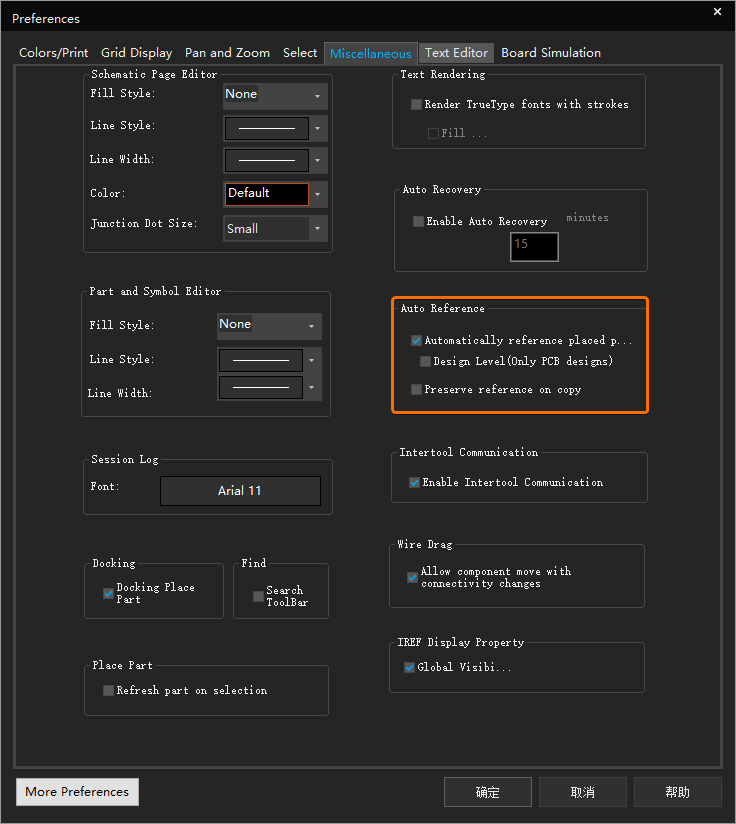

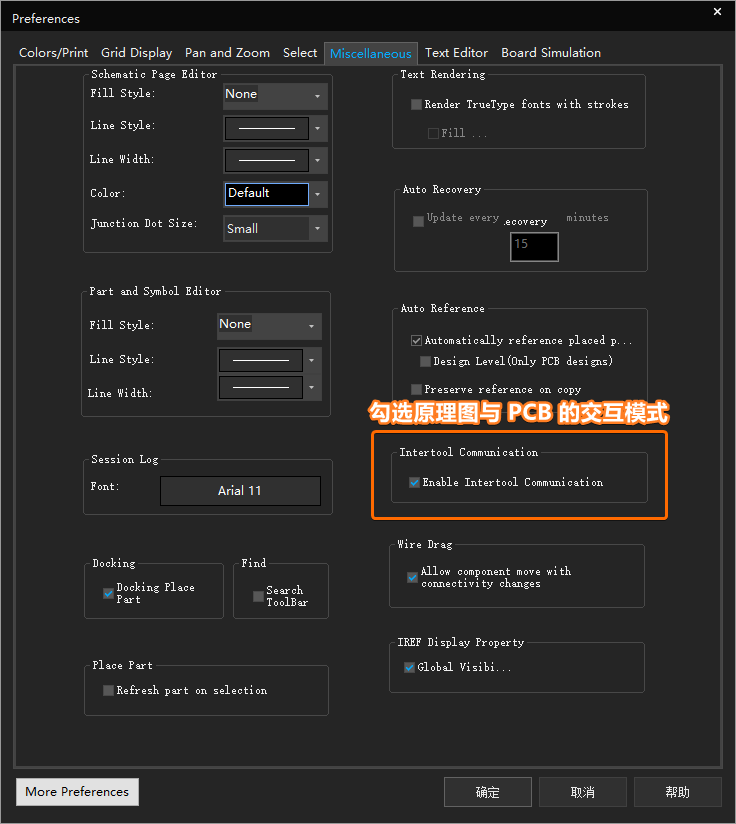

最后,再切换至【Miscellaneous】选项卡,勾选 Auto

Reference 选项区的

Automatically reference placed,使得放置和复制粘贴原理图符号时能够自动填写位号:

注意:Miscellaneous [ˌmɪsəˈleɪniəs] 表示的是其它参数。

原理图符号的绘制

原理图工程下新建符号库

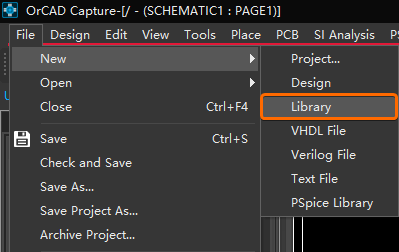

接下来,在上面新建的 UINIO-Cadence-Template

工程当中,鼠标依次点击 OrCAD Capture CIS

菜单栏上的【File -> New ->

Library...】,新建一个原理图符号库:

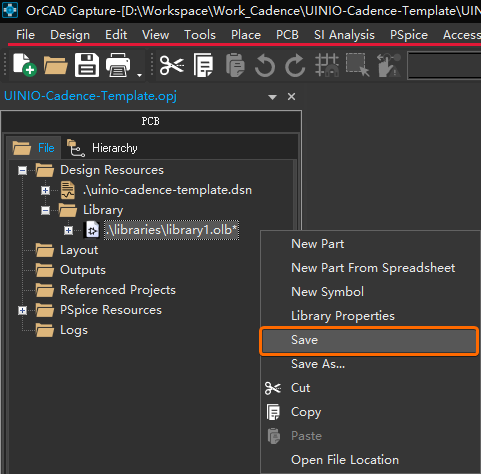

默认情况下,新建的原理图符号库名称叫做

LIBRARY1.OLB,选中这个符号库单击鼠标右键,在弹出的菜单中选择【Save】或者【Save

As...】项:

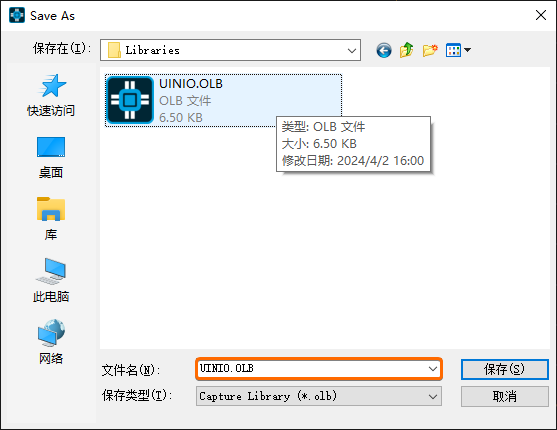

此时会弹出下面的对话框提示你选择一个保存位置,在这里我们将上面默认的原理符号库名称修改为

UINIO.OLB,并将其保存到 UINIO-Cadence-Template

工程的 Libraries 目录下面:

原理图符号库下新建符号

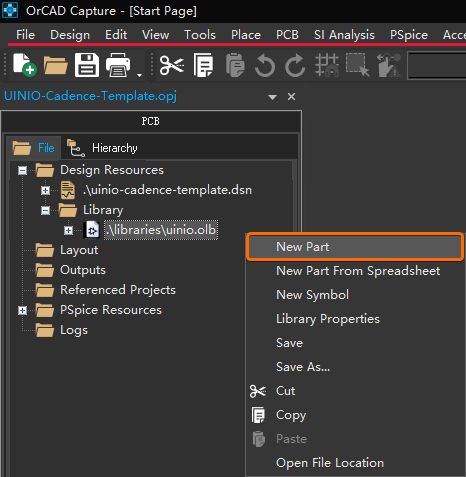

在 OrCAD Capture CIS

左侧的工程列表当中,再次选中修改名称之后的

UINIO.OLB。按下鼠标右键并点击弹出菜单当中的【New

Part】,新建一个原理图符号:

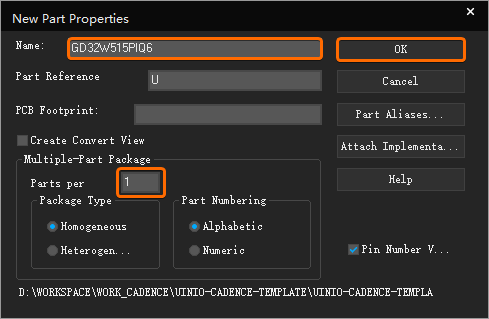

此时会弹出 New Part Properties

对话框,需要再继续填写原理图符号的名称(这里假设为GD32W515PIQ6),然后鼠标点击【OK】按钮:

在上面对话框当中,OrCAD Capture CIS

会将原理图符号的封装类型 Package Type 划分为

Homogeneous(默认)和 Heterogeneous 两种:

- Homogeneous [ˌhɒməˈdʒiːniəs] 同种类构成元器件:由多个相同的 Part 组成,只需要创建其中一个部分,其它部分就会自动与其保持一致。

- Heterogeneous [ˌhetərəˈdʒiːniəs] 多种类构成元器件:由多个不同的 Part 组成,多用于引脚数量较多的 IC 元器件,可以对引脚进行分组分块设计,以便于后期的原理图设计。

注意:这些 Part 的具体数量,都是由上面对话框当中的【Parts per】项控制。如果当前符号具有多个 Part,那么就可以通过菜单栏上的 【View -> Next Part】或者快捷键 【Ctrl + N】,以及【View -> Previous Part】或者快捷键 【Ctrl + P】,在这个原理图符号的不同 Part 之间来回进行切换。

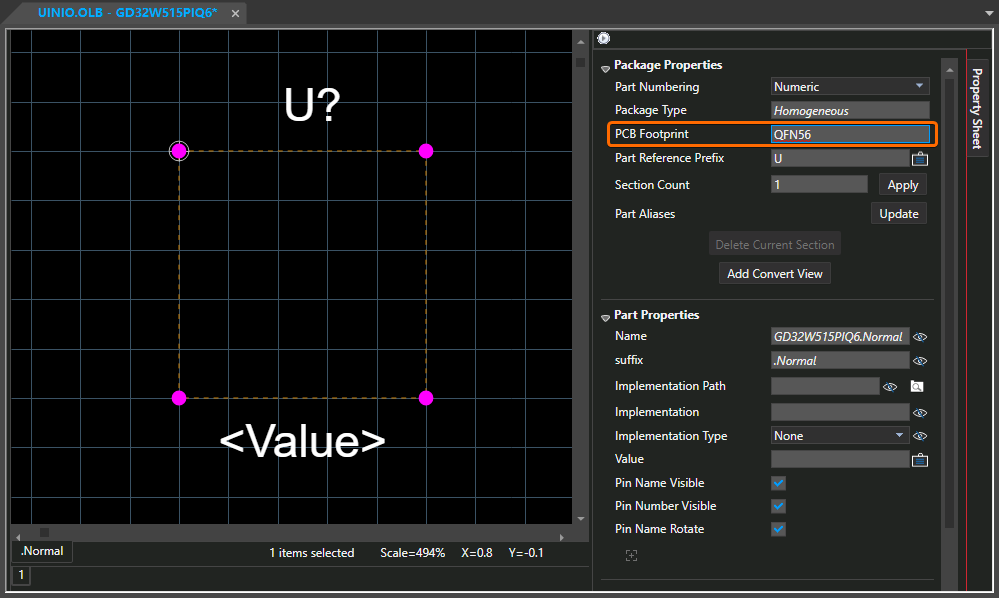

开始绘制原理图符号

完成前面的操作步骤之后,就可以通过调节 OrCAD Capture

CIS

主界面工作区当中的元器件虚线框,去控制原理图符号的大小尺寸。当鼠标点选该虚线框的时候,其四个边角上面就会分别出现紫色圆点,鼠标按住拖动就可以进行调节(下图右侧属性区的

PCB Footprint 字段,用于关联该原理图符号所对应的 PCB

封装):

注意:在 OrCAD Capture CIS 工作区按下字母【I】可以进行放大(Zoom In),也可以按下字母【O】进行缩小(Zoom Out)操作。

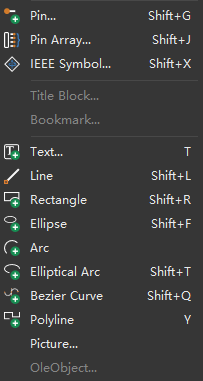

接下来,展开菜单栏上的【Place】选项(如下图所示),或者点击 OrCAD Capture CIS 右侧绘制工具栏上的对应图标,就可以在虚线框里面绘制原理图符号的形状并且放置引脚:

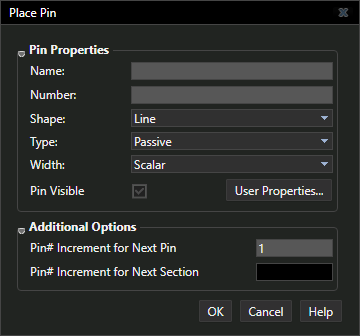

借助上述工具绘制完原理图符号的形状之后,就要开始放置原理图符号的引脚,这里鼠标选择菜单栏上的【Place -> Pin】,或者按下快捷键【Shift + G】,再或者点击最右侧绘制工具栏上的【Place pin】按钮,此时会弹出 Place Pin 对话框:

Place Pin 对话框当中,各个属性的功能说明如下面列表所示:

Name:引脚名称。Number:引脚编号。Shape:引脚的形状类型。Type:引脚信号输入/输出属性。Width:引脚的显示宽度。

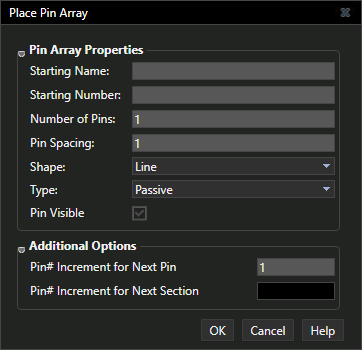

如果需要批量放置多个引脚,则可以鼠标点击菜单栏上的【Place -> Pin Array】或者按下【Shift + J】快捷键,在弹出的 Place Pin Array 对话框进行如下设置:

Place Pin Array 对话框当中,各个属性的功能说明如下面列表所示:

Starting Name:第一个引脚的名称。Starting Number:第一个引脚的编号。Number of Pins:需要放置的引脚总数。Pin Spacing:引脚之间的间隔距离。Pin# Increment for Next Pin:引脚 Name 和 Number 的递增量。

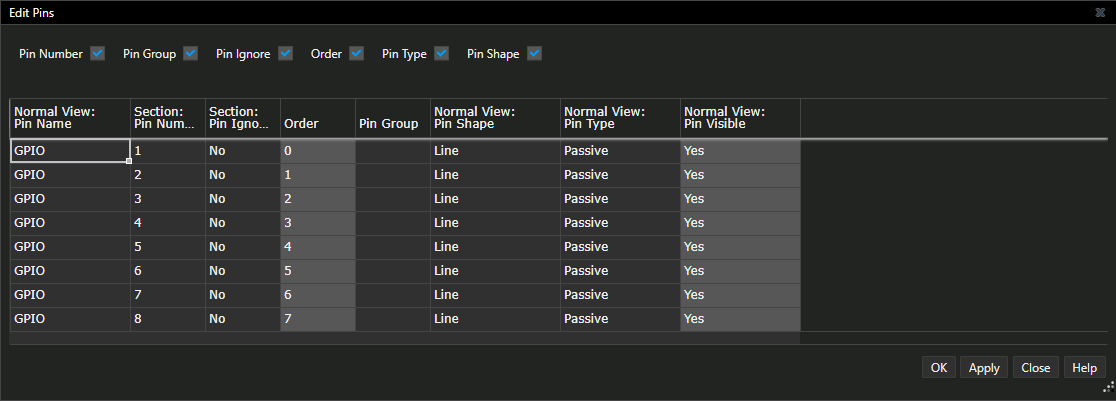

除此之外,在选中原理图工作区当中的一个或者多个引脚之后,点击鼠标右键菜单中的【Edit Pins】,或者直接按下快捷键【Shift + H】,就可以批量修改该原理图符号的各个引脚属性:

这个时候在 UINIO-Cadence-Template

目录下,呈现出的工程文件结构如下面所示,可以发现上面新建的

Libraries 目录,以及该目录下新增的 UINIO.OLB

符号库文件:

1 | └─UINIO-Cadence-Template |

注意:完成原理图符号的外形绘制以及引脚放置之后,可以按下快捷键【Ctrl + S】执行保存操作,或者在工作区的窗口标签上展开鼠标右键菜单,选择【Save】项执行保存操作。

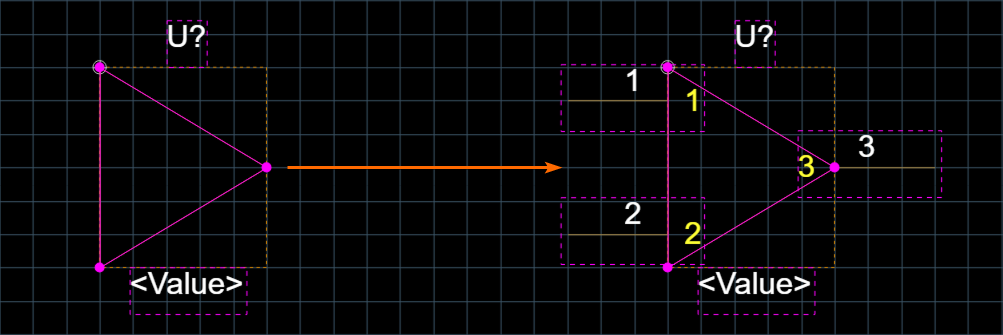

在紫色的虚线图框当中,绘制完原理图符号(下图左),并且完成引脚的放置(下图右)之后,所得到的效果如下面所示:

注意:原理图符号相关的图形,必须放置在紫色的虚线框当中。

常用快捷键汇总

| 快捷键 | 功能说明 | 快捷键 | 功能说明 |

|---|---|---|---|

| 【I】 | 缩小工作区内容。 | 【Shift + G】 | 放置一个原理图符号引脚。 |

| 【O】 | 放大工作区内容。 | 【Shift + J】 | 批量放置多个原理图符号引脚。 |

| 【Ctrl + S】 | 保存操作。 | 【Shift + H】 | 修改原理图符号引脚属性。 |

| 【Ctrl + N】 | 切换至下一个原理图符号的 Part。 | 【Ctrl + P】 | 切换至上一个原理图符号的 Part。 |

开始原理图的绘制

自动备份设置

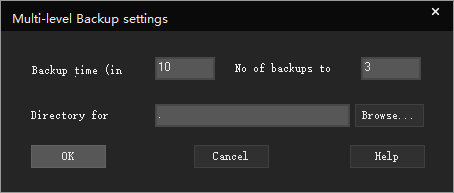

选择 OrCAD Capture CIS 主界面菜单栏上的【Options -> Autobackup】,此时会弹出下面的 Multi-level Backup settings 对话框:

在弹出的 Multi-level Backup settings 对话框里,可以进行如下选项的设置:

- Backup time:自动备份时间,默认为 10 分钟。

- No of backups to:自动备份保存个数,默认为 3 个。

- Directory for:自动备份保存路径(建议指定一个目录,避免找不到备份文件)。

原理图图框全局设置

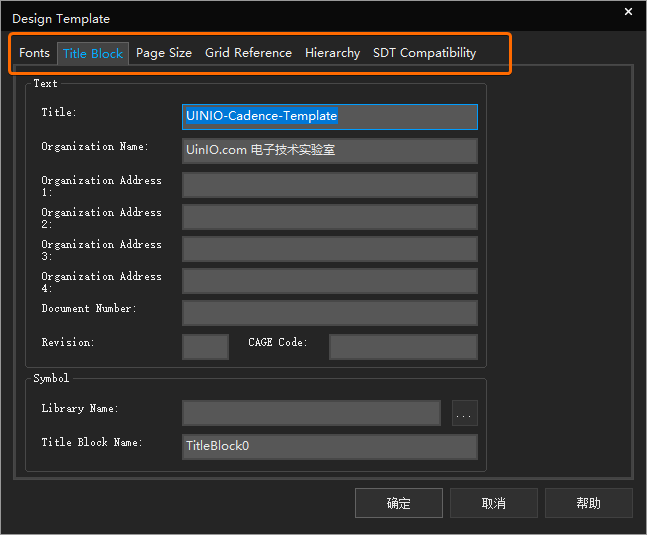

选择 OrCAD Capture CIS 主界面菜单栏上的【Options -> Design Template】,此时会弹出下面的 Design Template 对话框:

在上面弹出的 Design Template 对话框当中,可以选择如下的几个选项卡进行设置:

- Fonts:模板默认的字体。

- Title Block:设置原理图右下角边框区域的模板。

- Page Size:页面大小设置(只对新建的原理图页面有效)。

- Grid Reference:配置工作区顶部和左侧显示的网格参考符。

- Hierarchy:层级设置(保持默认即可)。

- SDT Compatibility:SDT 文件兼容性(保持默认即可)。

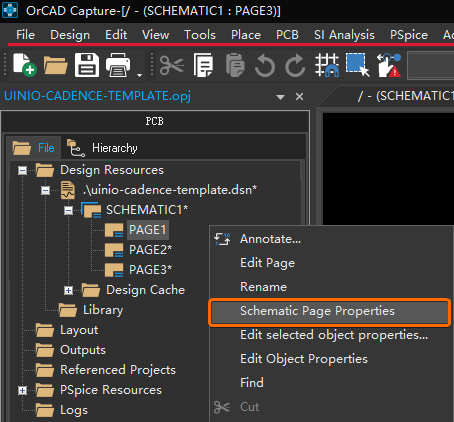

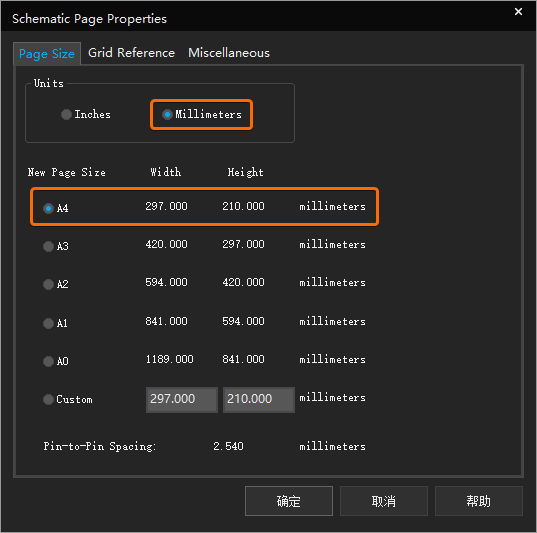

修改指定原理图页面的属性

首先,鼠标选中需要修改的那一页原理图,单击鼠标右键并且选择 Schematic Page Properties 项:

然后,在弹出的 Schematic Page Properties 窗口当中,就可以设置该原理图的各种属性:

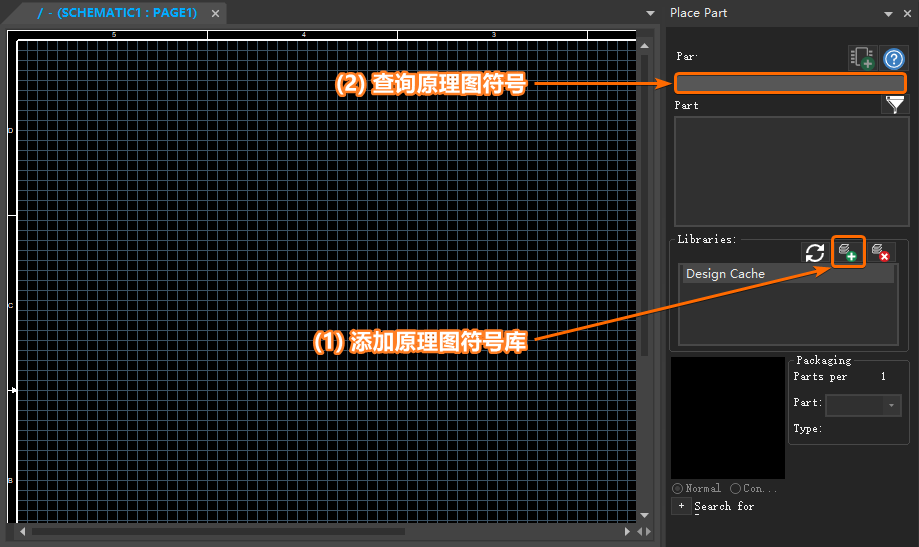

添加原理图符号库 & 符号

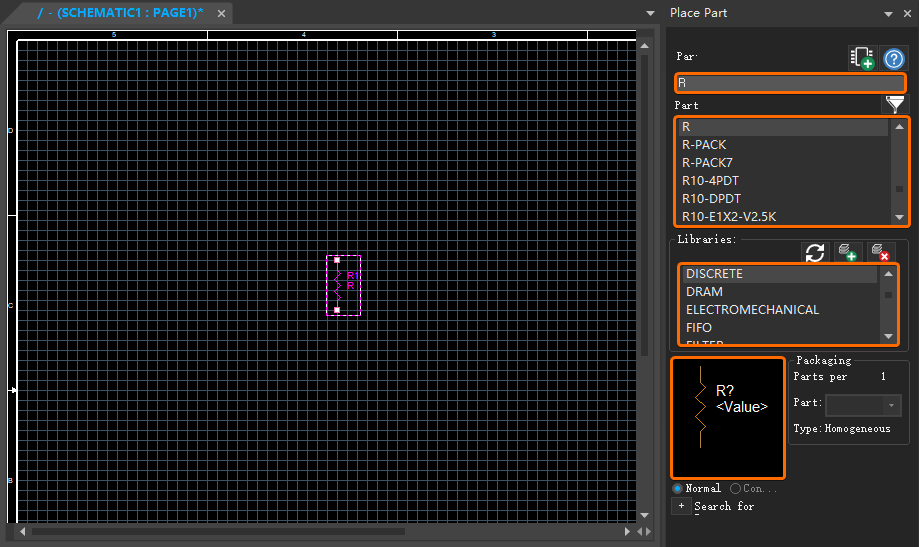

第一次打开刚才新建的原理图的时候,选择 OrCAD Capture CIS 主界面菜单栏上的 【Place -> Part】,或者直接按下快捷键 P,此时就会在主界面右侧弹出原理图符号列表:

首先,鼠标点击上图 (1)

的按钮添加原理图符号库,OrCAD Capture CIS 自带有 46 个

.olb 原理图库文件,都保存在 Cadence SPB

安装目录下的

D:\Software\Tech\Cadence\SPB_17.4\tools\capture\library

文件夹当中。其中

CAPSYM.olb、CONNECTOR.olb、DISCRETE.olb、TRANSISTOR.olb

这几个库最为常用:

CAPSYM.olb:存放电源、地、输入输出端口、标题栏等。CONNECTOR.olb:存放有各种各样的连接器。DISCRETE.olb:存放电阻、电容、电感、开关、变压器等常用分立(Discrete [dɪˈskriːt])元件。TRANSISTOR.olb:存放 FET、UJT、PUT 等晶体管元件。

然后,就可以在上图 (2)

的输入框里搜索指定元件,比如这里就放置了一个 DISCRETE.olb

原理图符号库当中的电阻

R。在选择好原理图符号之后,在工作区双击鼠标进行摆放,然后按下快捷键【ESC】或者选中鼠标右键菜单的【End

Mode】结束摆放):

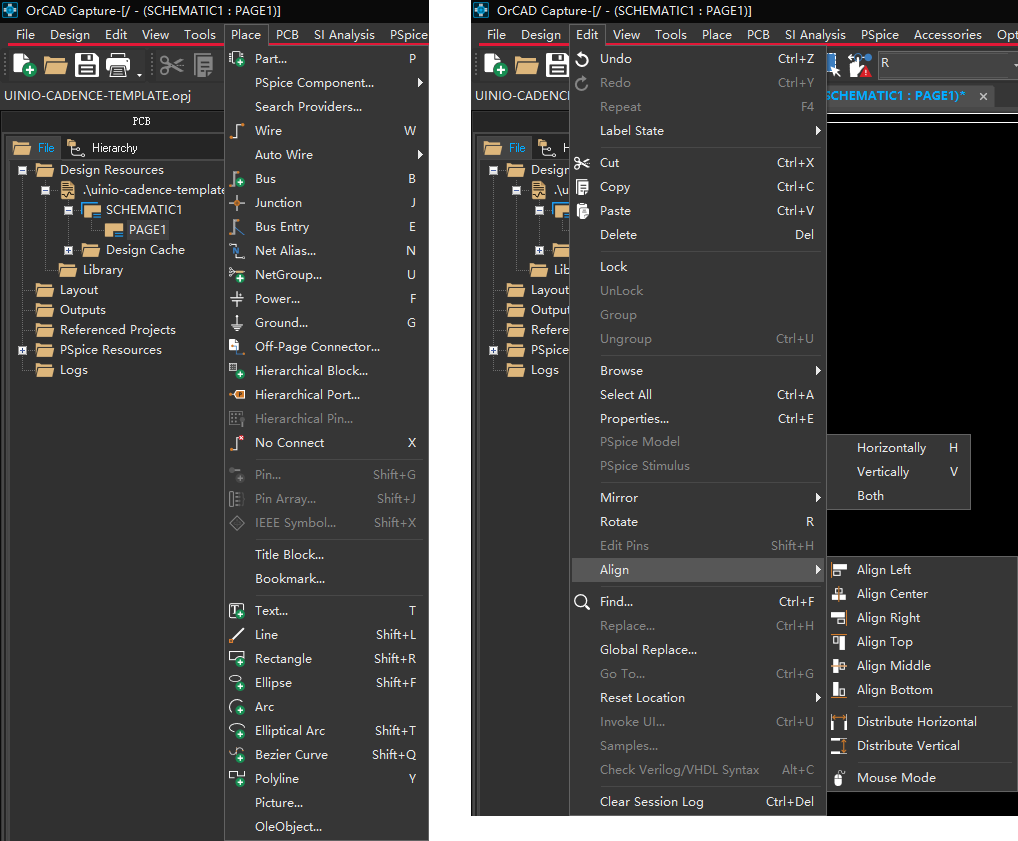

原理图符号的相关操作,主要集中在 OrCAD Capture CIS 菜单栏的【Edit】项下面。而连接原理图符号、绘制辅助线、添加文字图片的各种操作,则主要集中在菜单栏的【Place】项下面:

原理图符号的各种操作

| 原理图符号操作 | 具体操作方式说明 |

|---|---|

| 选择 | 被鼠标选中之后,原理图符号周围会出现紫色虚线框。 |

| 移动 | 首先选中原理图符号,然后鼠标左键按下拖动即可。 |

| 对齐 | 执行菜单栏上的【Edit -> Align -> Align Left/Center/Right/Top/Middle/Bottom】项。 |

| 镜像 | 执行菜单栏上的【Edit -> Mirror -> Horizontally/Vertically/Both】项,或者按下快捷键【H】或者【V】。 |

| 旋转 | 执行菜单栏上的【Edit -> Rotate】命令,或者直接按下快捷键【R】。 |

| 拖动复制 | 选中符号,按下按键【Ctrl】直接拖动,松开鼠标即可快速完成复制粘贴操作。 |

| 删除 | 首先选中符号,然后按下快捷键【Delete】。 |

| 复制 | 选中符号,鼠标右键选择【Copy】,或者直接按下快捷键【Ctrl + C】。 |

| 剪切 | 选中符号,鼠标右键选择【Cut】,或者直接按下快捷键【Ctrl + X】。 |

| 粘贴 | 选中符号,鼠标右键选择【Paste】,或者直接按下快捷键【Ctrl + V】。 |

| 撤销操作 | 直接按下快捷键【Ctrl + Z】。 |

| 重做操作 | 直接按下快捷键【Ctrl + Y】。 |

电气连接相关的操作

| 原理图电气连接操作 | 具体操作方式说明 |

|---|---|

| 绘制导线 | 点击菜单栏命令【Place -> Wire】,或者按下快捷键【W】。 |

| 结束导线绘制 | 按下快捷键【Esc】,或者鼠标右键菜单选择【End Wire】项。 |

| 添加连接结点 | 在两条交叉未连接的导线之间添加连接节点,可以执行菜单栏命令【Place -> Junction】,或者按下快捷键【J】。 |

| 放置网络标号 | 点击菜单栏上的【Place -> Net Alias】,或者直接按下快捷键【N】。 |

| 忽略 ERC 检查点 | 点击菜单栏上的【Place -> No Connect】,或者直接按下快捷键【X】。 |

| 总线 | 点击菜单栏【Place ->

Bus】或快捷键【B】(总线名称格式为 名称 + [],例如

BUS[0:5]、BUS[0-5]、BUS[0...5])。 |

| 总线分支 | 点击菜单栏上的【Place -> Bus

Entry】,或者按下快捷键【E】(总线分支名称格式为

总线名称 + 序数,例如

BUS0、BUS1)。 |

| 放置电源 | 点击菜单栏上的【Place -> Power】,或者按下快捷键【F】。 |

| 放置地 | 点击菜单栏上的【Place -> Ground】,或者按下快捷键【G】。 |

| 跨页连接符 | 点击菜单栏上的【Place -> Off-Page Connector】,或者按下快捷键【G】。 |

| 差分标识 | 鼠标选中需要添加差分标识的原理图页,再点击菜单栏上的【Tools -> Create Differential Pair】。 |

放置非电气对象

OrCAD Capture CIS 原理图当中的辅助线,可以用于标识信号和原理图功能模块。

| 非电气对象放置操作 | 具体操作方式说明 |

|---|---|

| 修改辅助线属性 | 通过鼠标双击辅助线,可以修改辅助线的属性。 |

| 放置辅助线(直线) | 点击菜单栏【Place -> Line】,或按下快捷键【Shift + L】。 |

| 放置辅助线(矩形) | 点击菜单栏【Place -> Rectangle】,或按下快捷键【Shift + R】。 |

| 放置辅助线(椭圆线) | 点击菜单栏【Place -> Ellipse】,或按下快捷键【Shift + F】。 |

| 放置辅助线(椭圆弧线) | 点击菜单栏【Place -> Elliptical Arc】,或按下快捷键【Shift + T】。 |

| 放置辅助线(贝塞尔曲线) | 点击菜单栏【Place -> Bezier Curve】,或按下快捷键【Shift + Q】。 |

| 放置辅助线(折线 ) | 点击菜单栏【Place -> Polyline】,或按下快捷键【Y】。 |

| 放置辅助线(弧线) | 选择菜单栏上的【Place -> Arc】项。 |

| 放置图片 | 选择菜单栏上的【Place -> Picture...】项。 |

| 放置字符标注 | 选择菜单栏【Place -> Text...】,或按下快捷键【Shift + T】。 |

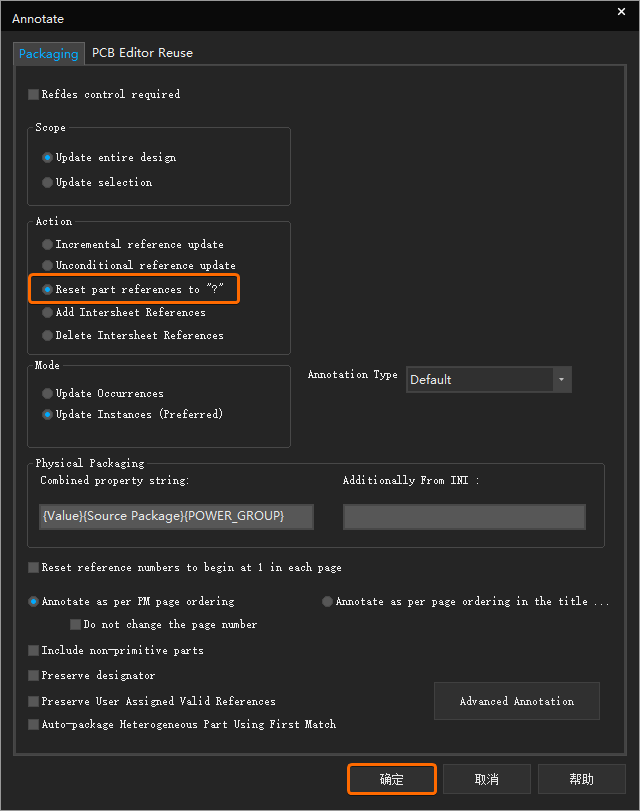

重新生成原理图符号的位号

首先,需要清除原理图上原有的位号,鼠标选择 OrCAD Capture

CIS 菜单栏上的【Tools -> Annotate】,勾选弹出对话框当中的

Reset part references to "?"

选项,然后按下【确定】按钮,就可以复位当前原理图上的所有位号:

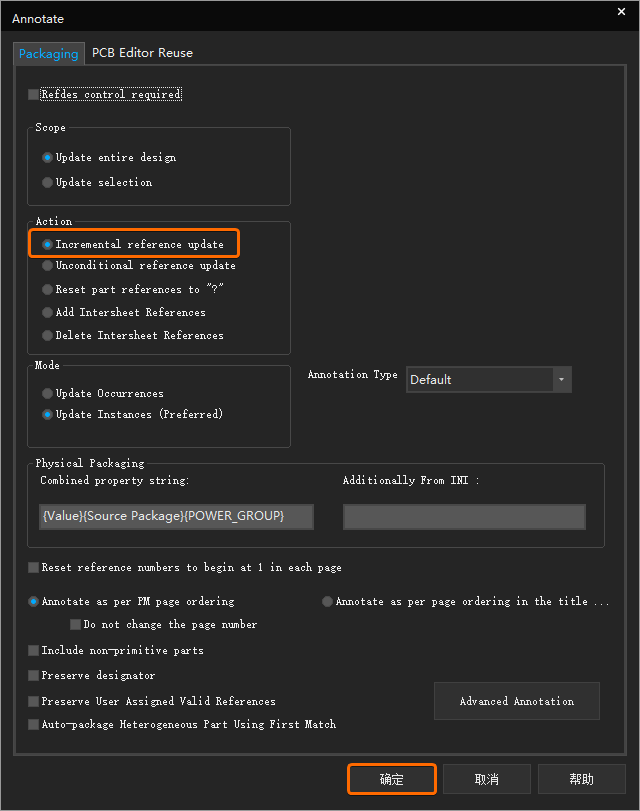

然后,就可以重新生成原理图上所有符号的位号,这里依然点击菜单栏上的【Tools

-> Annotate】项,勾选弹出对话框当中的

Incremental reference update

选项,然后按下【确定】按钮,就可以为当前原理图上的所有符号重新生成位号:

调整原理图符号属性表格显示方式

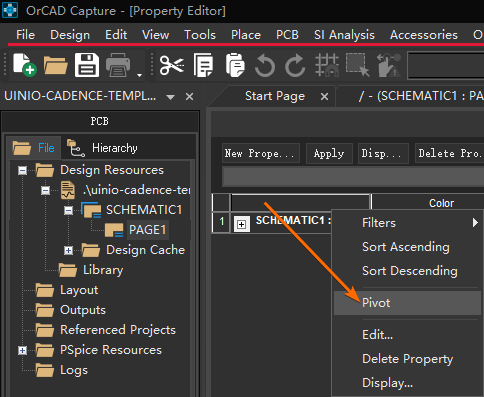

在 OrCAD Capture CIS 的工作区,鼠标双击原理图符号,就会进入到属性编辑器【Property Editor】界面,该界面当中的属性表格默认是横向显示,查阅起来十分不便。因此可以鼠标右键单击下图当中标识的位置,选择弹出菜单中的【Pivot】选项:

此时,就可以将属性表格的显示方向更换为纵向,这样阅读起来会更加的直观与方便(按照上述的步骤重新操作一次,就可以重新切换回横向显示模式):

注意:英文 Pivot [ˈpɪvət] 指的是数据透视表。

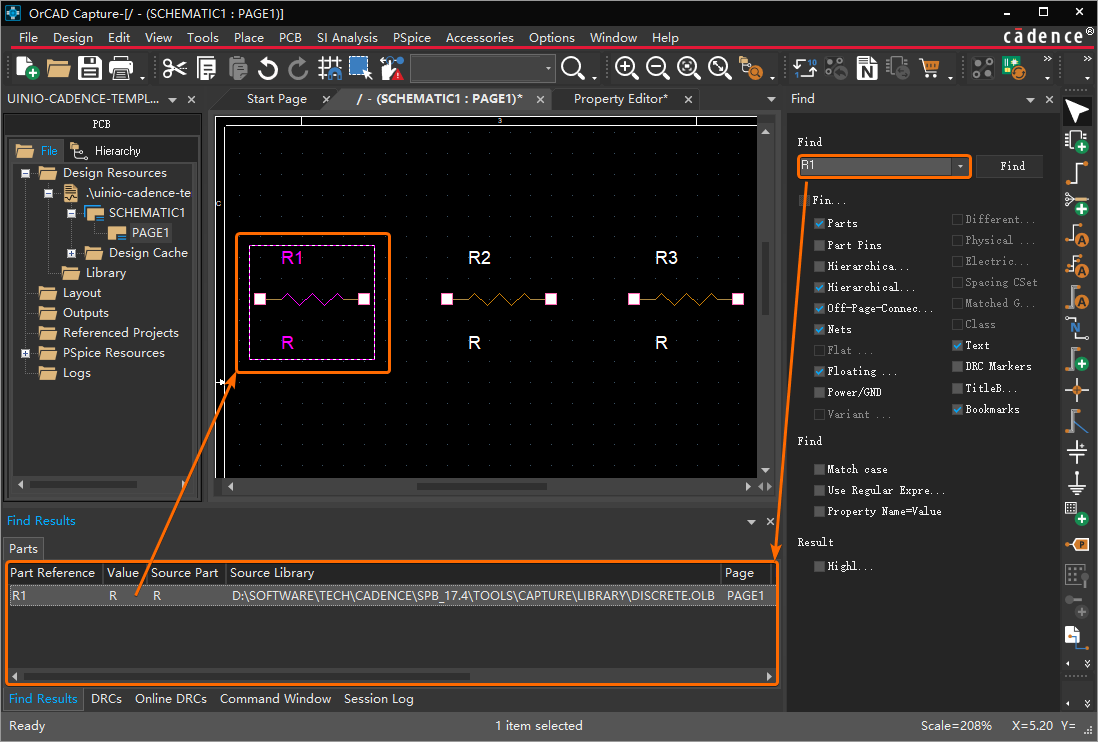

搜索原理图或者工程

鼠标点击 OrCAD Capture CIS 菜单栏上的【Edit ->

Find】项,或者直接按下快捷键【Ctrl + F】,就可以在主界面工作区右侧展开

Find

工作面板,在这里可以查询到原理图范围或者工程范围的位号、字符、网络标号、引脚编号等内容。

搜索结果会展示在 OrCAD Capture CIS 底部的状态信息显示区域,此时使用鼠标双击该区域的某一条查询结果,就会自动高亮原理图当中与查询结果匹配的符号,具体操作步骤可以参考上面的示意图。

层次原理图的设计

复杂的电路设计只绘制一张原理图,可读性会非常差,这种情况下可以采用层次化的原理图结构来提升可读性,即将复杂电路按照功能划分为若干的子模块。使得设计人员前期可以按照模块进行设计,最后通过在这些子模块原理图之间建立连接关系来完成整个电路的设计。层次原理图的设计方法,主要划分为自上而下和自下而上两种:

- 自上而下的方式:先绘制顶层模块的原理图,再绘制子层模块的原理图。

- 自下而上的方式:先绘制子层模块的原理图,再绘制顶层模块的原理图。

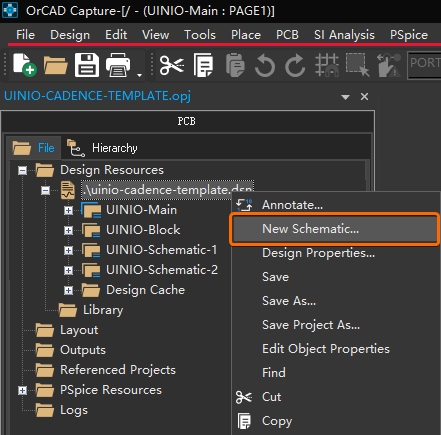

新建一个原理图模块

在 OrCAD Capture CIS 左侧工程列表当中的

.\uinio-cadence-template.dsn

原理图上面点击鼠标右键,选择展开菜单中的【New

Schematic...】新建一个名称为 UINIO-Main

的原理图模块(默认名称为

SCHEMATIC1,可以自定义名称):

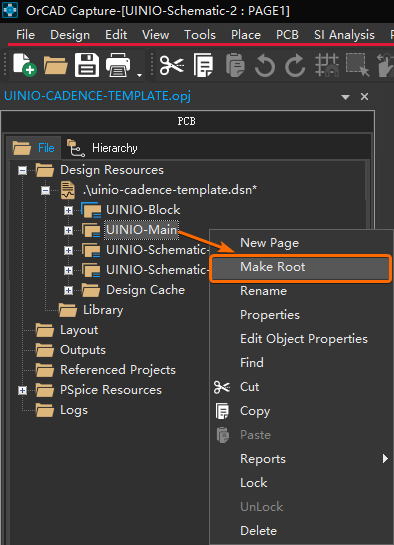

指定根原理图模块

OrCAD Capture CIS 当中的每一份原理图,都需要指定一个

root 根模块。选中左侧工程列表当中的 UINIO-Main

模块,然后点击鼠标右键执行【Make Root】,把上面新建的

UINIO-Main 指定为根模块:

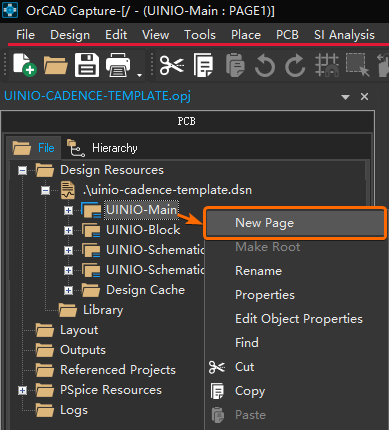

新建一个原理图页

在 OrCAD Capture CIS 左侧工程列表当中的

UINIO-Main 上面点击鼠标右键,选择展开菜单中的【New

Page】新建一张原理图页(默认名称为

PAGE1,可以自定义名称):

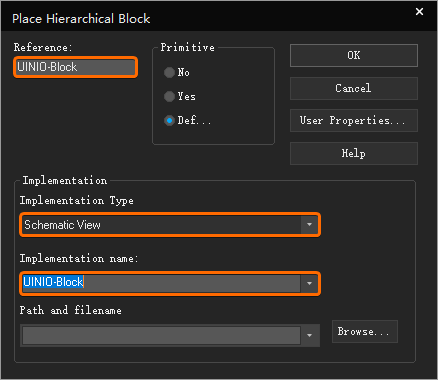

自上而下的层次原理图设计

首先,在 OrCAD Capture CIS 左侧建立并且打开

UINIO-Main/PAGE1 原理图页,执行菜单栏上的【Place ->

Hierarchical

Block...】命令,在弹出的对话框中输入分层模块的名称

UINIO-Block,并且选择合适的参数:

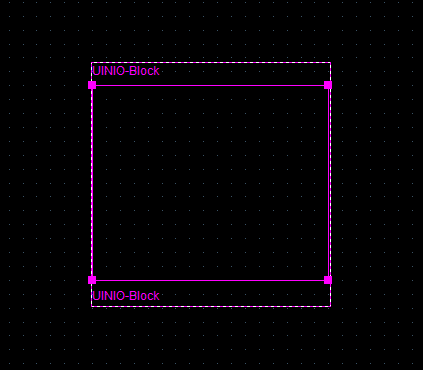

然后,在该原理图工作区放置分层模块框,并且将其拖动至合适的大小,以便于后续放置分层端口:

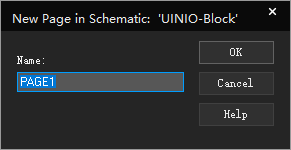

接着,鼠标双击上面的分层模块框,或者选择鼠标右键菜单中的【Descend

Hierarchy】项,设置好子层模块原理图的名称,这里使用默认的

PAGE1:

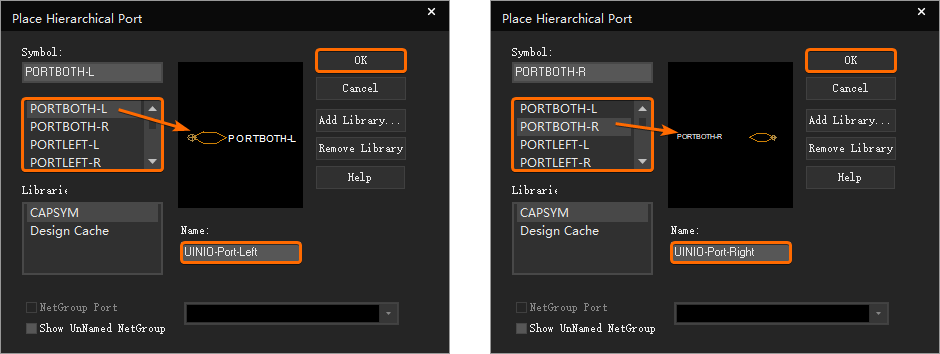

接下来,就可以在新生成的 UINIO-Block/PAGE1

原理图当中展开绘制工作,此时可以选择菜单栏上的【Place -> Hierarchical

Port...】项,在打开的对话框中选择对应的分层端口符号与名称(UINIO-Port-Left/Right):

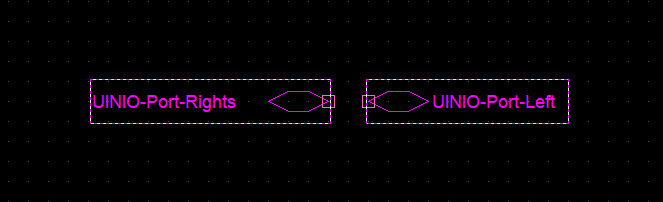

这里的分层端口主要用于与上一层模块建立关联,经过上述步骤放置到工作区原理图上的分层端口如下面所示:

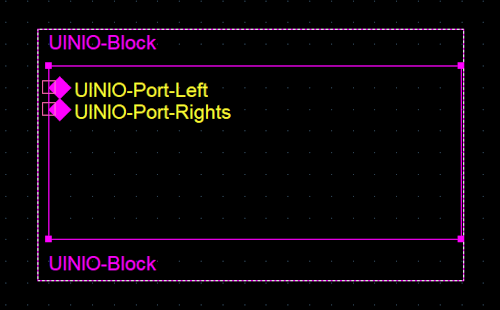

返回之前放置分层模块 UINIO-Block

的原理图工作区,选中模块之后展开鼠标右键菜单,点击【Synchronize

Up】选项,同步子层模块当中定义的分层端口至顶层模块当中:

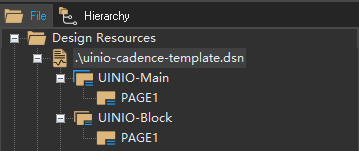

最后,OrCAD Capture CIS 左侧工程列表,所呈现出的自上而下层次原理图结构,如下面的截图所示:

自下而上的层次原理图设计

首先,在 OrCAD Capture CIS 左侧工程列表当中的

.\uinio-cadence-template.dsn

里面,新建两个原理图分层模块

UINIO-Schematic-1 和

UINIO-Schematic-2,同时仍然将 UINIO-Main

指定为根模块:

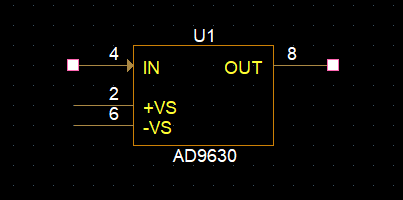

然后,在 UINIO-Schematic-1 和

UINIO-Schematic-2 两个原理图模块下的 PAGE1

页分别放置一个 AD9630 放大器元件:

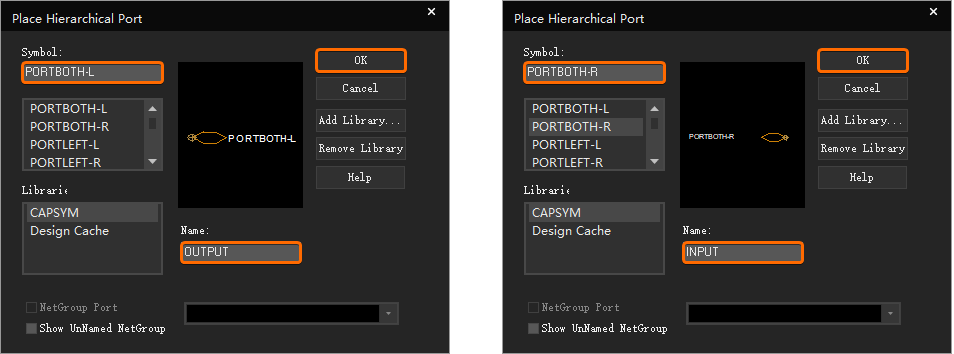

接着选择菜单栏上的【Place -> Hierarchical Port...】项,分别为

UINIO-Schematic-1/PAGE1 和

UINIO-Schematic-2/PAGE1 当中的 AD9630

添加输入输出相关的分层端口 INPUT 和

OUTPUT:

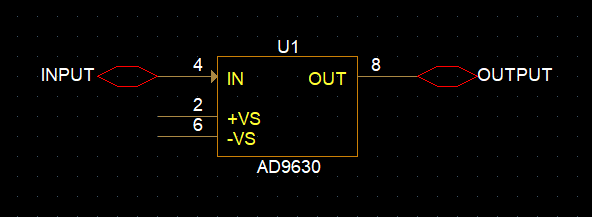

最终,原理图页 UINIO-Schematic-1/PAGE1 和

UINIO-Schematic-2/PAGE1 当中的 AD9630

放大器元件符号如下图所示:

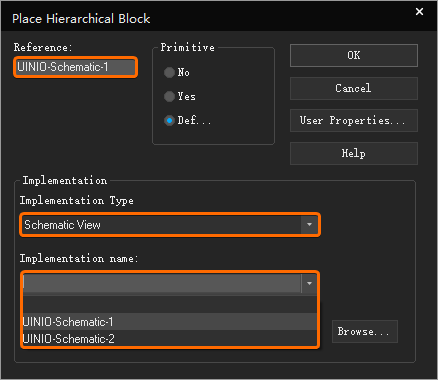

接下来,返回到根模块 UINIO-Main 的

PAGE1 原理图页,点击菜单栏上的【Place -> Hierarchical

Block...】,放置上面定义的 UINIO-Schematic-1 和

UINIO-Schematic-2 分层模块,注意在弹出的对话框当中选择

Schematic View,并且分别指定关联的原理图:

可以看到,此时放置的 UINIO-Schematic-1 和

UINIO-Schematic-2

分层模块,已经自带有分层端口(不需要再手动

Synchronize Up)。绘制导线连接两个分层模块的

INPUT 和 OUTPUT

端口,这样就完成了自下而上层次原理图的创建:

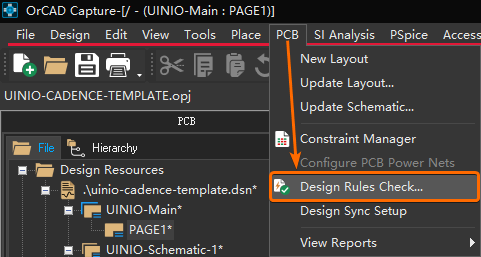

DRC 设计规则检查

生产环境当中,完成原理图的设计工作之后,在开始正式的 PCB 绘制之前,通常需要利用 OrCAD Capture CIS 提供的设计规则检查(DRC,Design Rules Check)功能进行查漏补缺。鼠标点击菜单上的【PCB -> Design Rules Check...】,就可以打开 DRC 检查对话框:

按下对话框当中的【Run】按钮,就可以开始运行 DRC 设计规则检查。检查当中发现的错误,都会展示在 OrCAD Capture CIS 底部的状态信息显示区域:

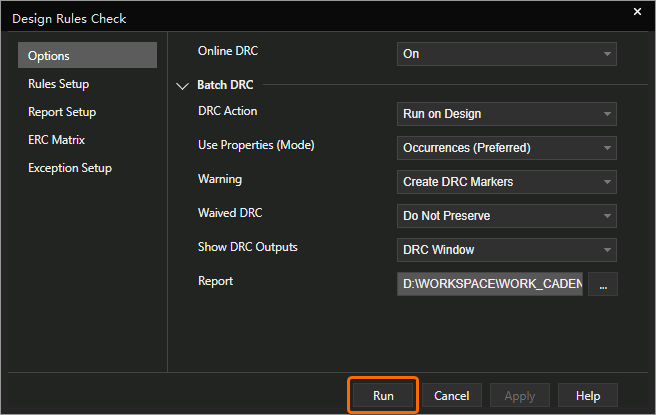

如果需要调整当前所要检查的设计规则,则只需要鼠标点击对话框左侧的【Rules Setup】标签,进行相应的勾选即可:

导出网表、BOM、PDF

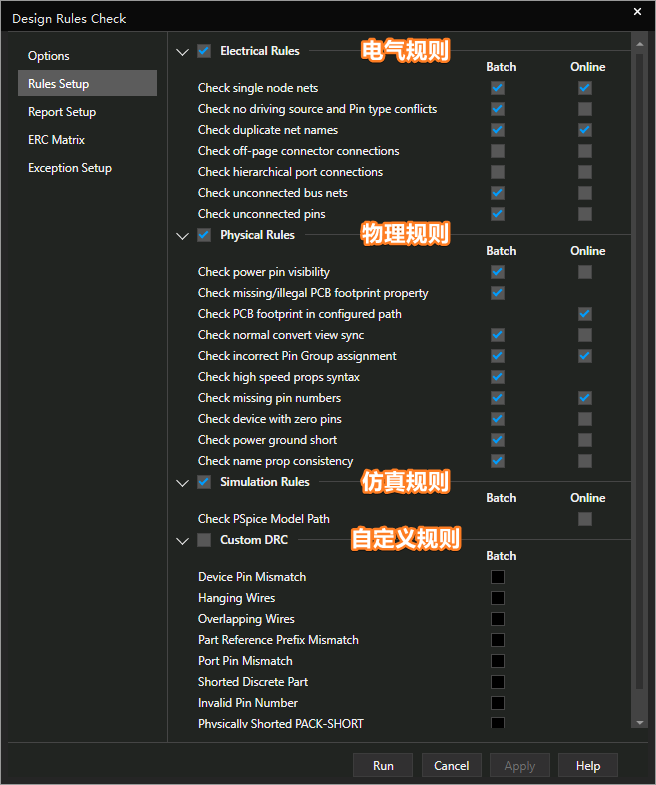

导出原理图对应的网表

网表(Netlist)用于保存原理图当中的电路网络连接关系,以及元件封装信息、位号映射关系等数据信息,并将这些信息同步到

PCB 版图。而 Cadence SPB SPB 17.4 已经支持原理图与 PCB

的同步更新,可以省略掉繁复的网表导出操作。

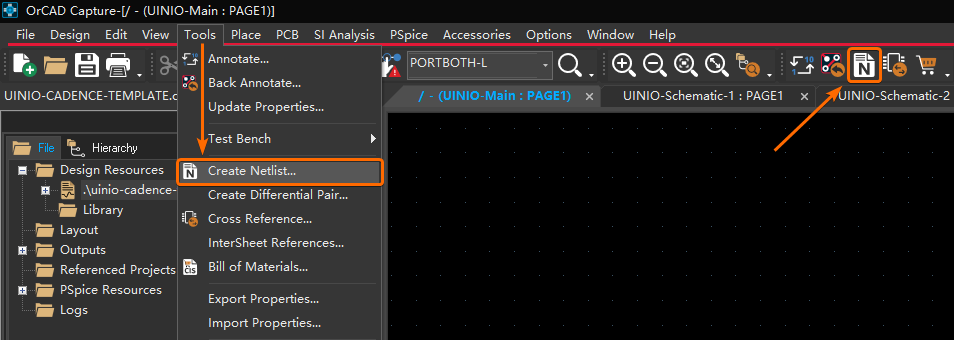

导出 Cadence SPB 网表

鼠标选择左侧工程列表当中需要生成网表的原理图文件(这里是

.\uinio-cadence-template.dsn),然后执行菜单栏命令【Tools

-> Create Netlist...】(也可以点击工具栏上的相应图标):

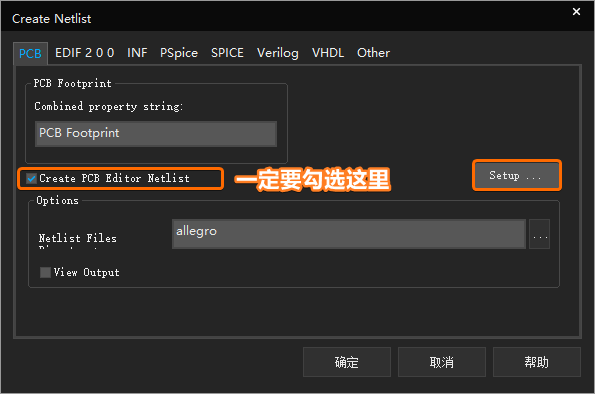

在弹出的【Create Netlist】对话框当中,勾选 PCB 选项卡下面的

Create PCB Editor Netlist,并且在【Netlist

Files】里输入网表文件的保存路径(默认为 allegro

文件夹):

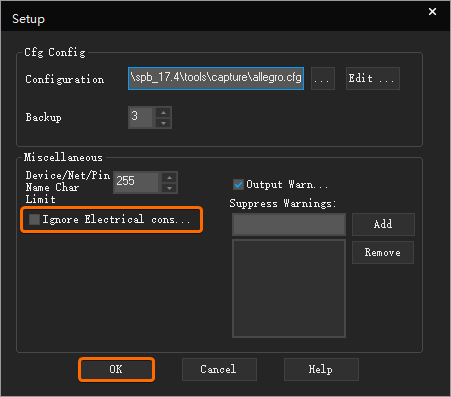

此时,如果单击该界面右侧的【Setup】按钮,在弹出的界面中勾选

Ignore Electrical Constraints

项,就会在导出过程当中忽略电气规则的检查(不建议这么做):

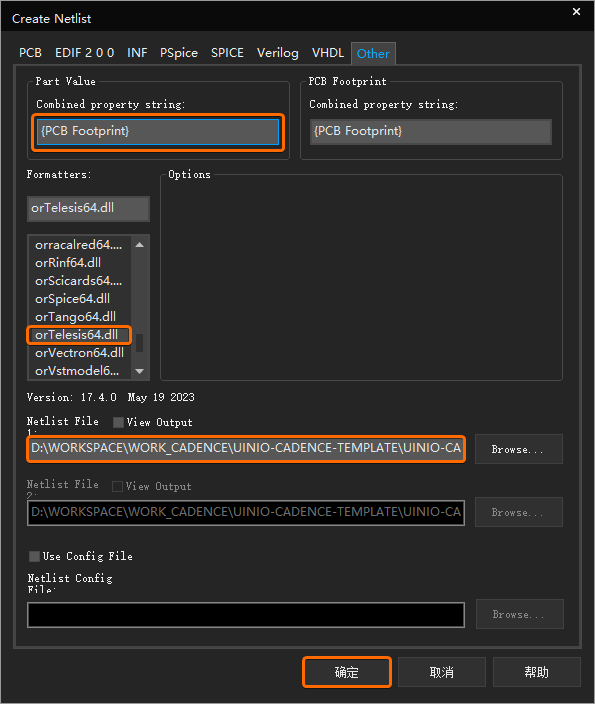

导出第三方网表

这里依然选择当前需要生成网表的原理图文件,然后同样鼠标点击菜单栏上的【Tools -> Create Netlist...】命令,在弹出的 Create Netlist 对话框当中,切换至【Other】选项卡:

此时需要在 Create Netlist 对话框当中,进行如下三个设置,才能够正确的导出第三方网表文件:

- 在 Formatters 栏中选择 orTelesis64.dll 选项。

- 在 Part Value 栏中填写

{PCB Footprint}(避免报错)。 - 在 Netlist File 栏填写第三方网表的导出路径。

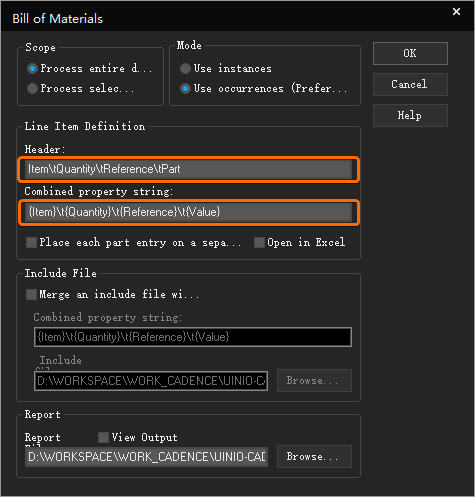

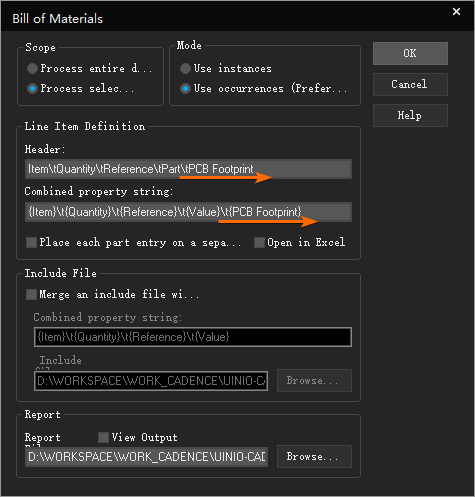

导出 BOM 清单

鼠标选择 OrCAD Capture CIS

左侧工程列表当中,当前需要生成网表的原理图文件(这里是

.\uinio-cadence-template.dsn),然后点击菜单栏【Tools ->

Bill of Materials...】导出该原理图的 BOM 清单:

注意该对话框当中 Line Item Definition 栏里的

Header 和 Combined property string

输入框,默认情况下分别填写的内容为

Item\tQuantity\tReference\tPart 和

{Item}\t{Quantity}\t{Reference}\t{Value},依次是元件数量、位号、属性值。但是缺省了元件封装相关的信息,因而需要在原来输入框内容的尾部分别再添加

\tPCB Footprint 和

\t{PCB Footprint},填写完成之后的界面如下图所示:

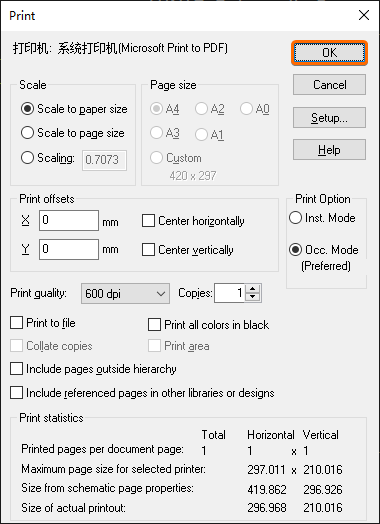

导出 PDF 格式的原理图

在 OrCAD Capture CIS

左侧的工程列表当中,选中当前需要生成网表的原理图文件(这里是

.\uinio-cadence-template.dsn)。打开菜单栏上的【Options

-> Preferences】项,在弹出对话框的【Colors/Print】选项卡下,选择打印

PDF

时需要输出的属性以及对应的颜色(通常情况下保持默认设置即可):

首先鼠标依次点击菜单栏上面的【File -> Print...】,或者直接按下快捷键【Ctrl + P】,然后在弹出的界面上点击【OK】,并在随后的操作系统对话框中选择 PDF 导出的位置以及 PDF 名称,从而完成原理图 PDF 的导出操作:

使用 Padstack 创建 .pad 焊盘

Cadence SPB 与其它板级 EDA

工具的一个最大区别就在于,使用 PCB Editor 17.4 创建 PCB

封装之前,需要先使用 Padstack Editor 17.4 工具制作好

.pad 焊盘文件,然后 PCB Editor

再导入这些焊盘,并且创建一个 .dra

可编辑封装工程,最后才能导出绘制 PCB 所使用的 .psm

封装文件:

1 | 焊盘文件(.pad) -> 可编辑封装文件(.dra) -> PCB 封装文件(.psm) |

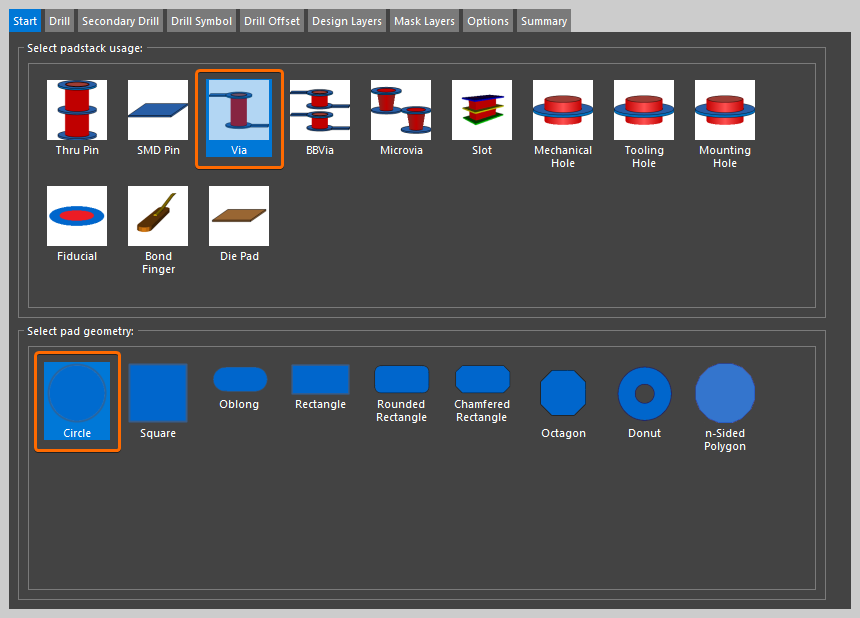

【Start】选项卡

选项卡【Start】是打开 Padstack Editor 工具之后的默认界面,在这里可以选择焊盘的用途与几何形状(根据当前选择的用途,只有支持该用途的 Padstack Editor 选项卡才可以被打开):

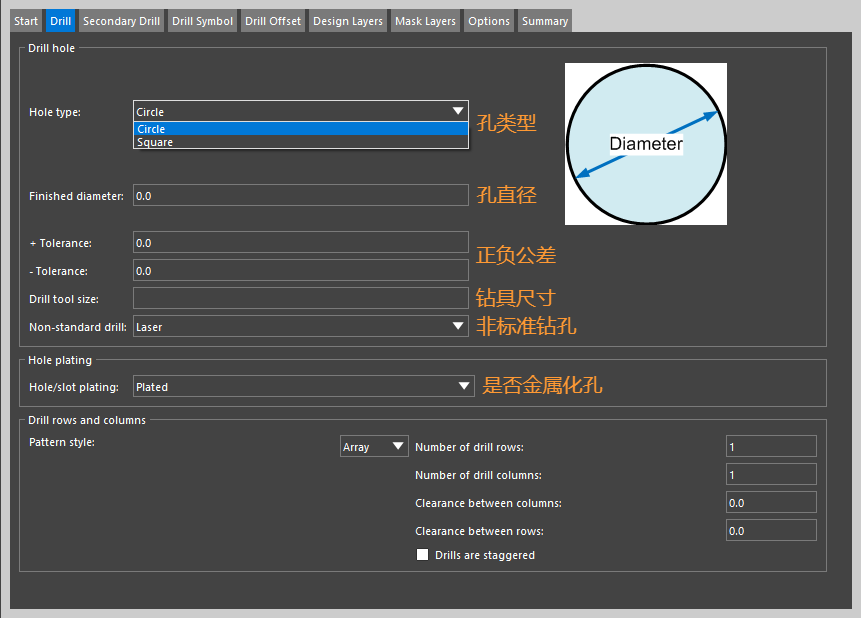

【Drill】选项卡

选项卡【Drill】里可以定义钻孔的类型、直径、公差,并且还支持一次性定义多个钻孔(需要在底部

Drill rows and columns

当中指定其行与列的信息):

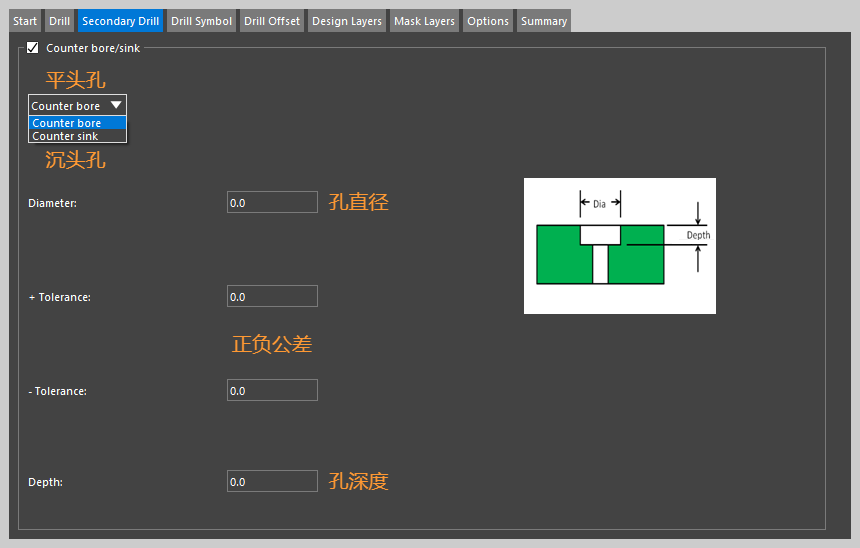

【Secondary Drill】选项卡

选项卡【Secondary

Drill】用于选择二次钻孔时所使用的是平头孔还是沉头孔,并且指定其

头部直径、公差、深度 参数:

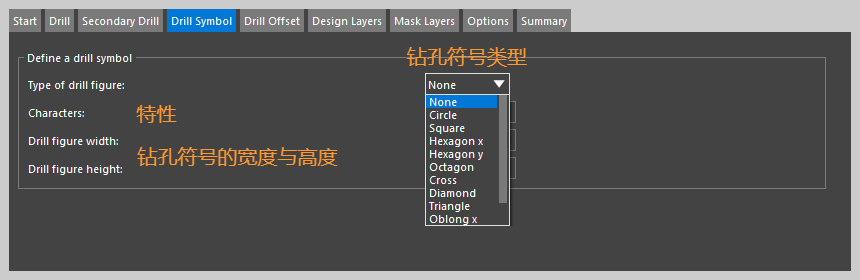

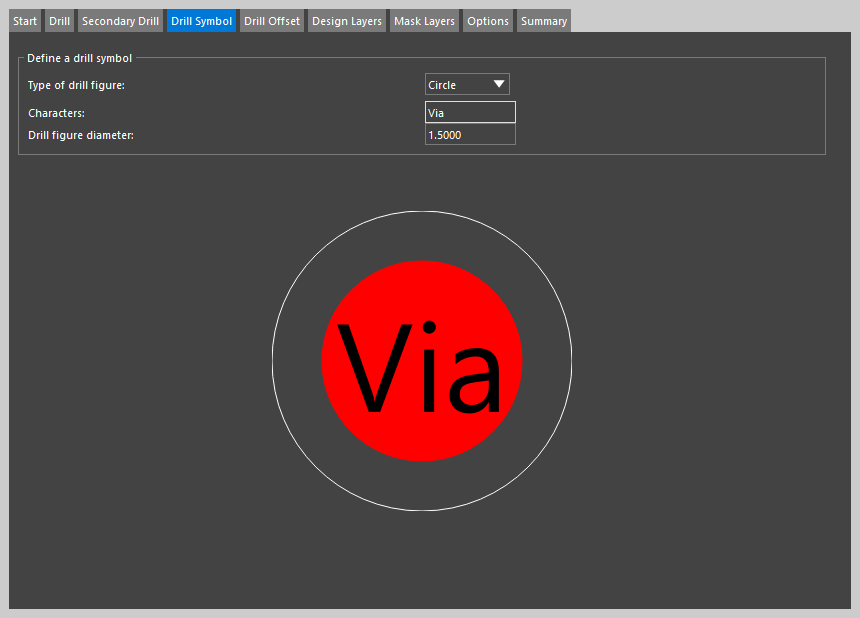

【Drill Symbol】选项卡

选项卡【Drill Symbol】可以设置用来标识钻孔的几何图形符号,即钻孔符号:

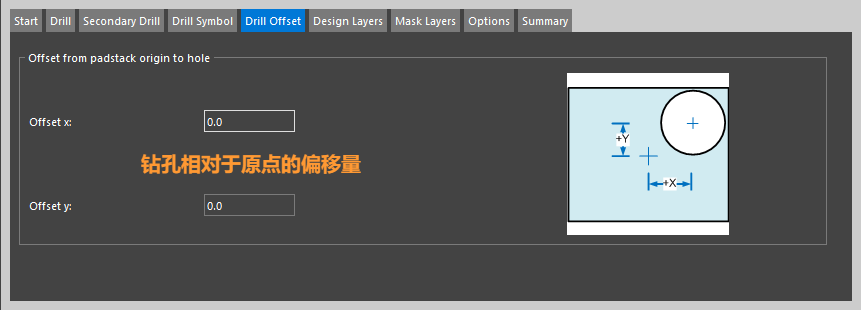

【Drill Offset】选项卡

选项卡【Drill Offset】下面的功能比较单一,仅用于定义钻孔相对于原点的位置偏移量:

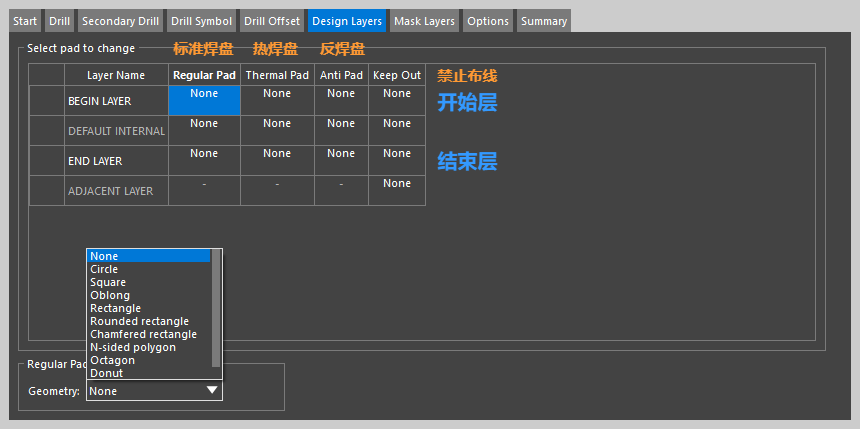

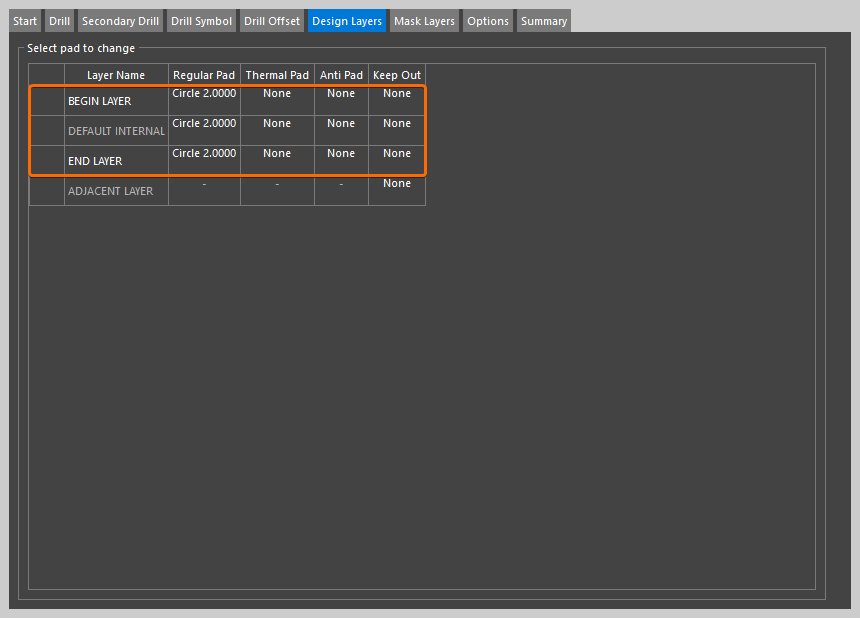

【Design Layers】选项卡

选项卡【Design Layers】用来设置焊盘在每一个叠层里的参数(通过鼠标右键菜单可以添加与删除叠层):

【Mask Layers】选项卡

选项卡【Mask Layers】用于设置焊盘在掩膜层相关的参数,可以通过右侧的【Add Layer】按钮添加更多的掩膜层(最多可以添加 16 次,一共 32 层):

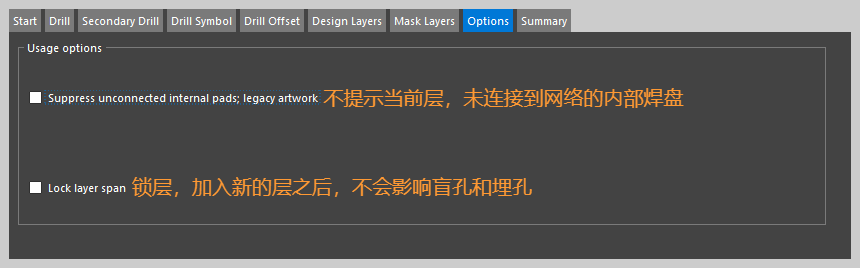

【Options】选项卡

选项卡【Options】里面只有如下两个选项,按需进行勾选即可:

制作 Via 过孔焊盘

接下来,我们使用 Padstack Editor 分别制作直径为

1.1mm、1.2mm、1.3mm

的三个过孔焊盘。首先在【Start】标签下,将 Padstack

Editor 的单位切换为

Millimeter,然后选择焊盘的用途为

Via,几何形状为 Circle:

在【Drill】标签下,设置孔的类型为 Circle,钻孔直径为

1.1mm,属于金属化孔

Plated:

在【Drill Symbol】标签下,钻孔符号名称设置为

Via,钻孔图形为 Circle,钻孔图形的直径为

1.5mm:

在【Design

Layers】标签下,可以对焊盘所涉及到的各个层进行设置(这里我们设置

BEGIN LAYER、DEFAULT INTERNAL、END LAYER

三个层):

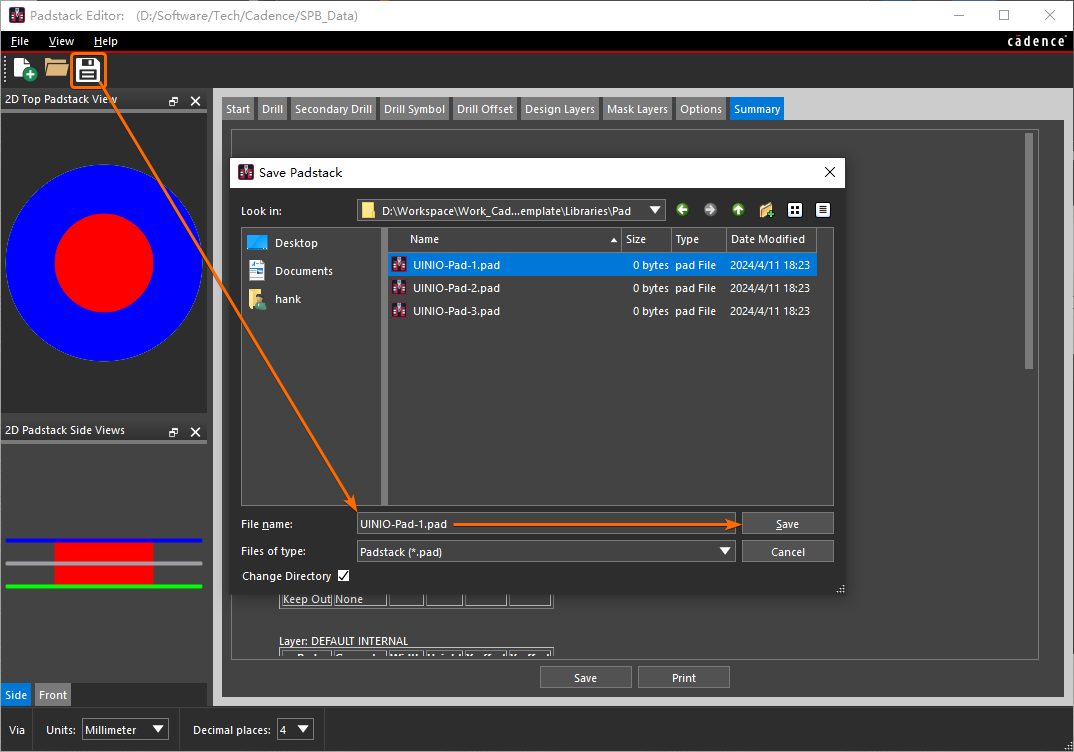

导出为 .pad 焊盘文件

选择好焊盘的用途以及形状,并且配置好相关参数之后,就可以点击

Padstack Editor 菜单栏上的【File -> Save/Save

As...】项,导出以 .pad

作为后缀的焊盘设计文件(将这些焊盘文件保存至

UINIO-Cadence-Template 工程下的 \Libraries\Pad

目录):

经过上述步骤制作完成直径分别为

1.1mm、1.2mm、1.3mm 的

UINIO-Pad-1.pad、UINIO-Pad-2.pad、UINIO-Pad-3.pad

三个焊盘文件以后,此时 UINIO-Cadence-Template

目录下所呈现的工程文件结构如下面所示:

1 | └─UINIO-Cadence-Template |

创建 .dra 工程制作 .pcm 封装

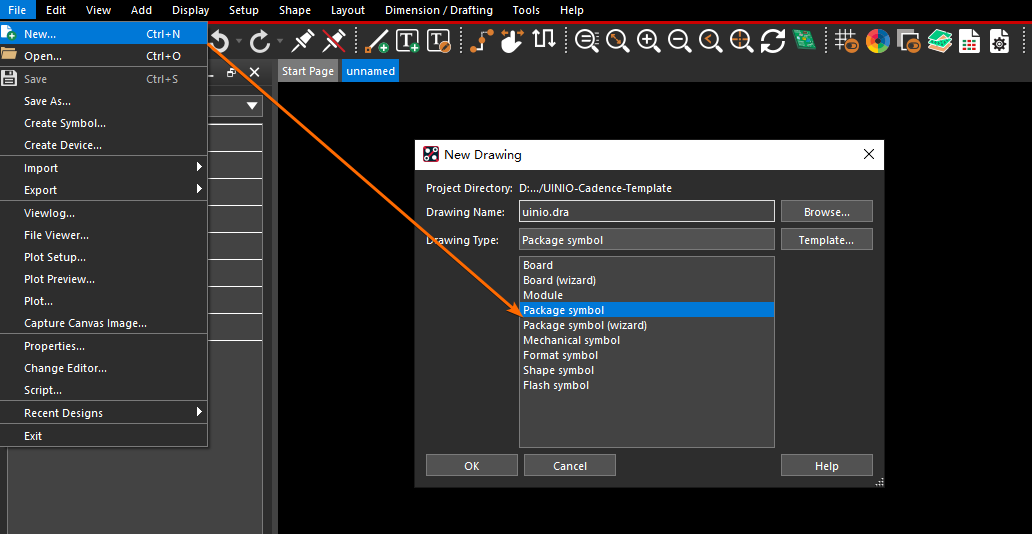

鼠标点击 Allegro PCB Editor 菜单栏上的【File -> New...】,此时可以选择如下两种 PCB 封装的创建方式:

- Package Symbol:基于 Padstack Editor 工具制作的焊盘来创建元件的 PCB 封装。

- Package Symbol (Wizard):基于向导的方式创建元件的 PCB 封装。

注意:该步骤创建的

.dra可编辑封装文件,可以保存到/Libraries/Footprint目录下面。

基于焊盘创建 PCB 封装

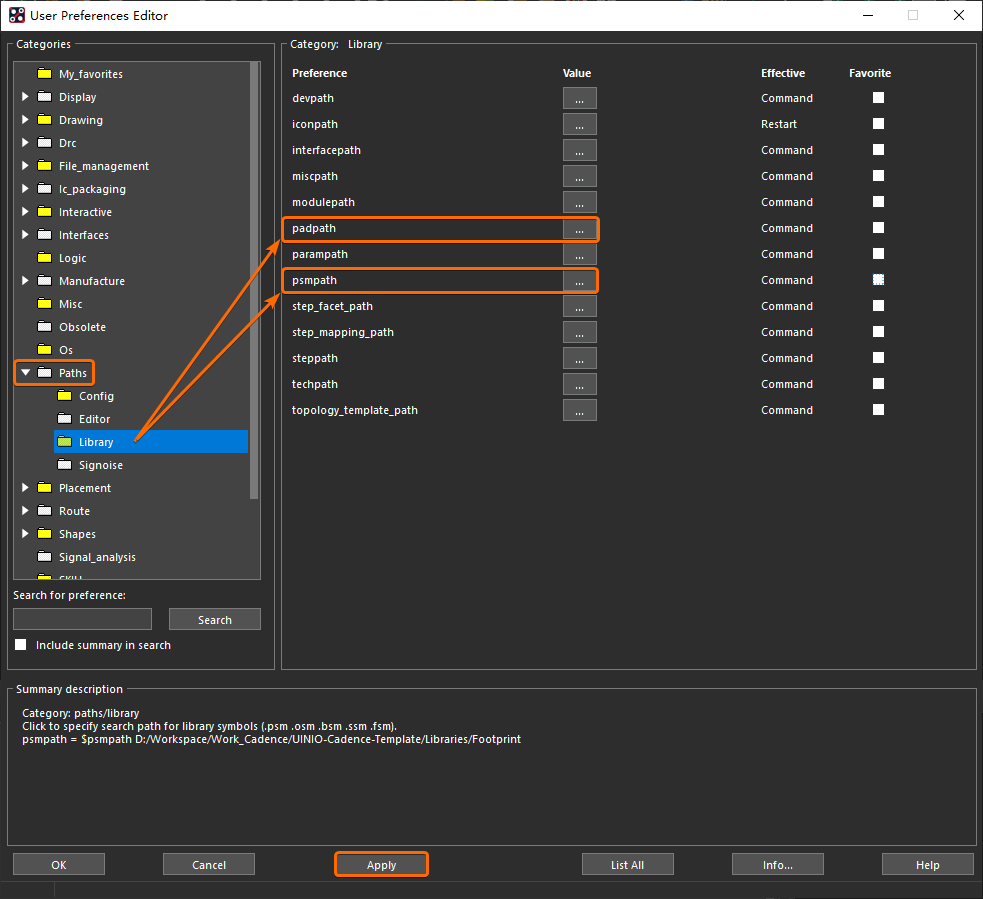

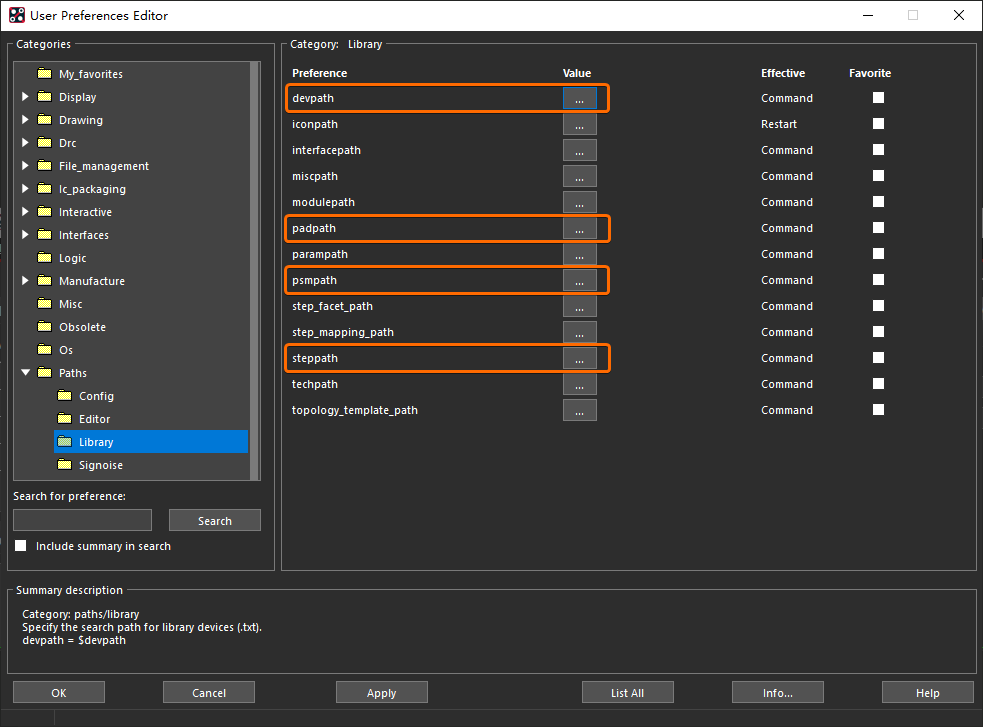

执行 Allegro PCB Editor 菜单栏上的【Set Up -> User Preferences】命令,在弹出的 User Preferences Editor 对话框依次点击【Path -> Library】:

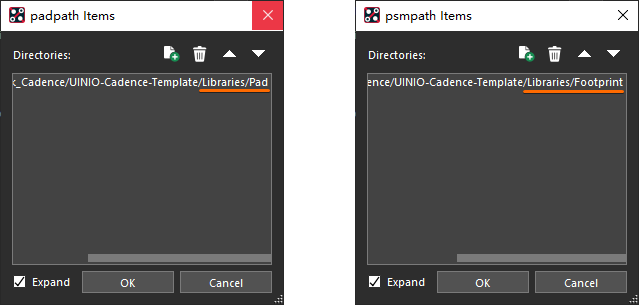

分别将焊盘文件路径 padpath

和封装文件路径 psmpath 指向

UINIO-Cadence-Template 工程下面预先建立好的

/Libraries/Pad(已经保存有之前 Padstack

Editor 导出的 .pad 焊盘文件)和

/Libraries/Footprint 目录,便于后期设计封装和 PCB

的时候,使用这些目录里保存的资源:

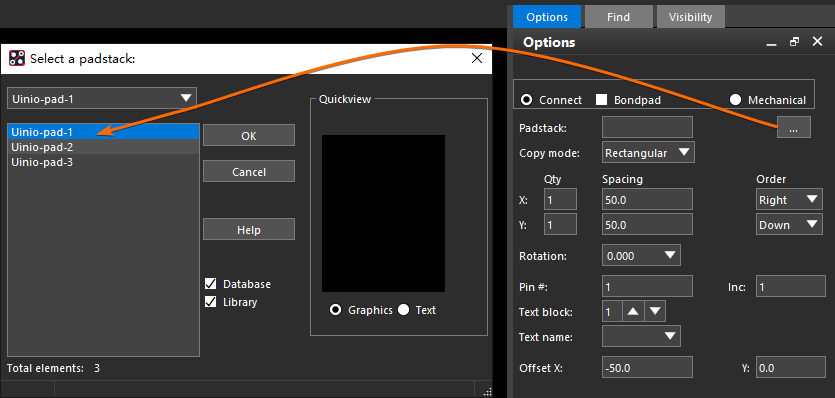

点击 Allegro PCB Editor 菜单栏上的【Layout ->

Pins】项,按下主界面右侧面板 Padstack

旁边的按钮,然后选择当前需要放置的 .pad 焊盘:

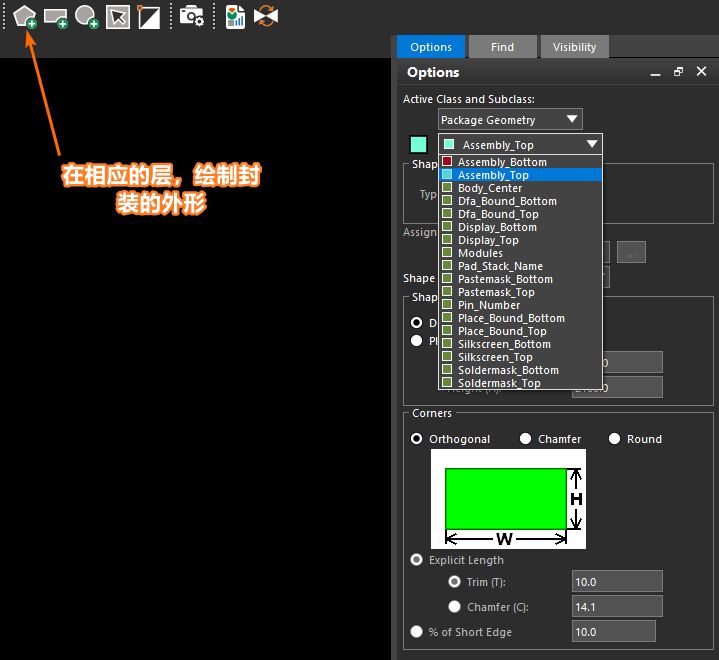

放置好焊盘之后,就可以选择工具栏上的【Shape Add】按钮,在右侧面板指定的层上面,放置各种封装相关的外形和文本信息:

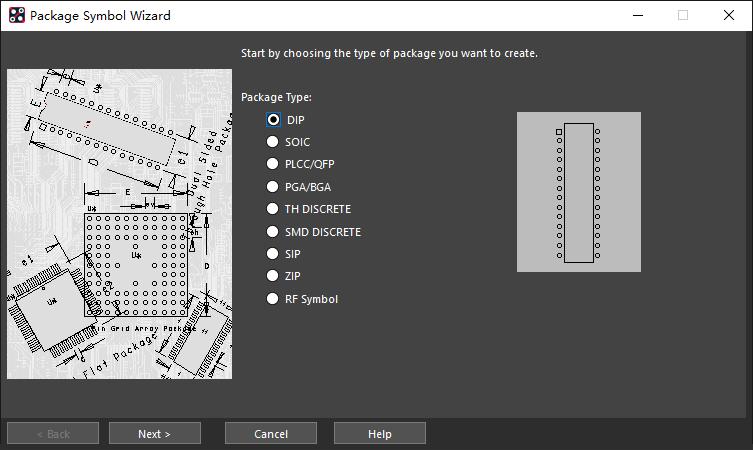

基于向导创建 PCB 封装

基于向导的方式创建元件的 PCB 封装,顾名思义就是基于如下 Package Symbol Wizard 对话框里面的向导步骤,逐步的去创建相应的 PCB 封装:

基于向导的方式去创建封装,可供选择的基本封装类型主要有如下八种:

| 序号 | 封装名称 | 封装中文 |

|---|---|---|

| 1 | DIP | 双列直插式封装。 |

| 2 | SOIC | 小外型集成电路封装。 |

| 3 | PLCC | 塑料芯片载体封装。 |

| 4 | QFP | 方形扁平封装。 |

| 5 | TH DISCRETE | 通孔分立元件封装。 |

| 6 | SMD DISCRETE | 贴片分立元件封装。 |

| 7 | SIP | 单列直插式封装。 |

| 8 | ZIP | 锯齿形直插式封装。 |

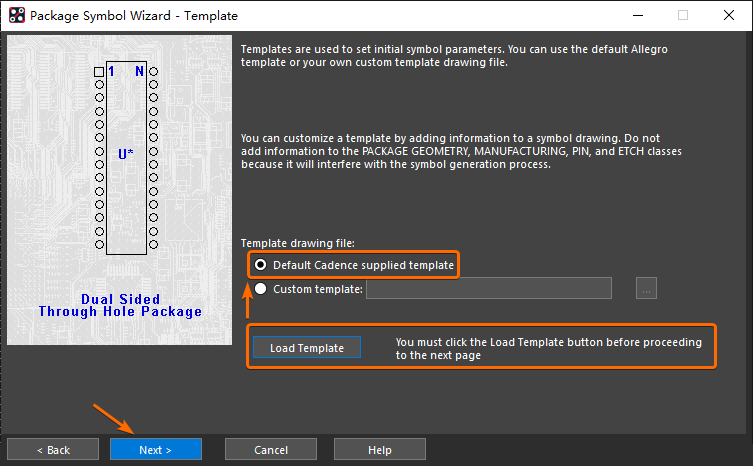

当鼠标点击 Package Symbol Wizard

对话框的【Next】按钮进行到下一个步骤的时候,需要首先点击该界面当中的【Load

Template】按钮,然后再勾选

Default Cadence supplied template

选项,接下来就可以继续点击【Next】进行进一步的配置:

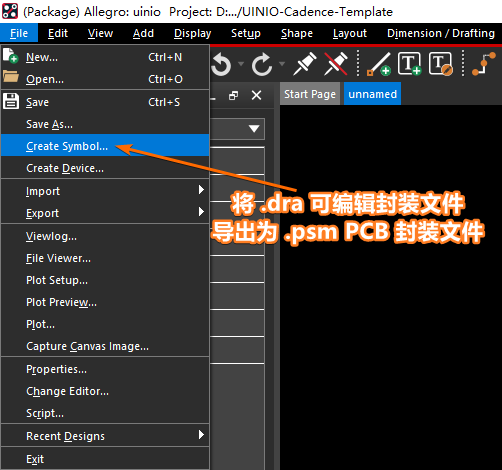

导出为 .psm 封装文件

接下来,鼠标点击【File -> Create Symbol...】项,将

.dra 可编辑封装文件导出为 .psm 格式的 PCB

封装文件(即 Allegro PCB Editor 绘制 PCB

时候所使用的封装文件):

注意:推荐将

.psm封装文件也保存至 UINIO-Cadence-Template 工程的\Libraries\Footprint目录下面。

当进行到这个阶段的时候,UINIO-Cadence-Template 目录下的工程文件结构就如下面所示:

1 | └─UINIO-Cadence-Template |

基于 PCB Editor 绘制版图

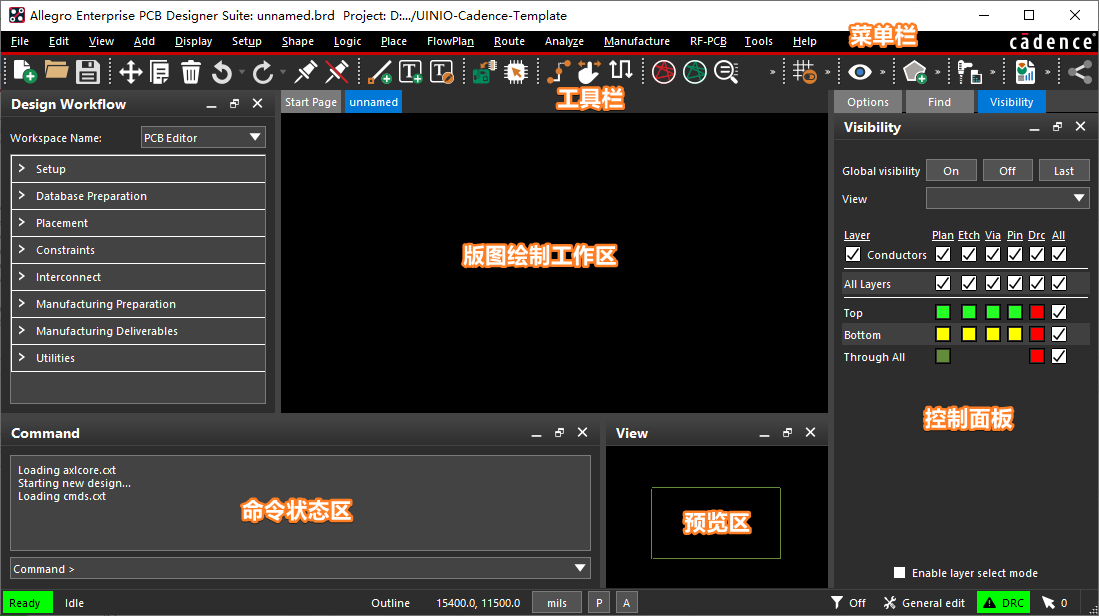

接下来的内容里,就可以开始使用 Allegro PCB Editor 进行版图布线了,其主界面视图主要包含有如下几个区域:

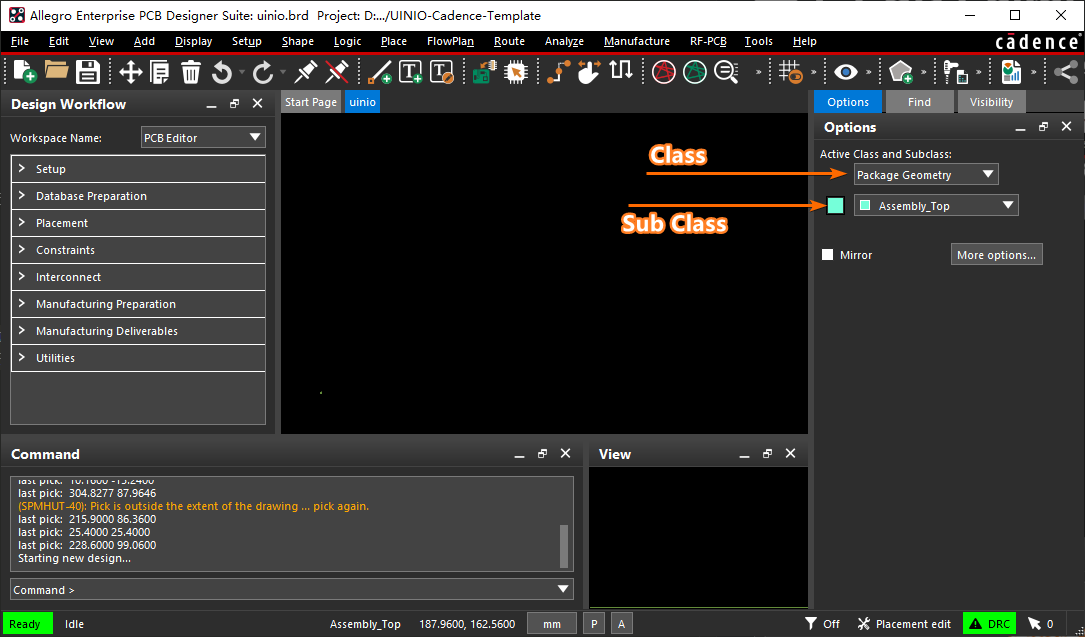

Class 与 Sub Class

Allegro PCB Editor 会将 PCB 划分为不同功能层次的组合,我们可以通过右侧控制面板上的【Options】进行切换:

这些功能层次按照 Class(类)和

Sub Class(子类)进行组织,例如比较常用的有

Board Geometry、Etch、Package

类及其子类:

| Board Geometry 类 | 功能描述 |

|---|---|

| Design outline 子类 | PCB 板框 |

| Dimension 子类 | 尺寸标注 |

| Silkscreen_top 子类 | 顶层丝印 |

| Silkscreen_bottom 子类 | 底层丝印 |

| Etch 类 | 功能描述 |

|---|---|

| top 子类 | 蚀刻顶层(走线与覆铜) |

| bottom 子类 | 蚀刻底层(走线与覆铜) |

| Package 类 | 功能描述 |

|---|---|

| Assembly_Top 子类、Assembly_Bottom 子类 | 装配层 |

| Pastemask_Top 子类、Pastemask_Bottom 子类 | 助焊层/钢网层 |

| Place_Bound_Top 子类、Place_Bound_Bottom 子类 | 元件封装的边界 |

| Silkscreen_Top 子类、Silkscreen_Bottom 子类 | 丝印层 |

| Pin_Number 子类 | 引脚编号 |

下面表格整理了 Allegro PCB Editor 当中

Class(类)和

Sub Class(子类)所涉及的英文术语:

| 英文术语 | 中文释义 | 英文术语 | 中文释义 |

|---|---|---|---|

| Active | 激活 | Class | 类 |

| SubClass | 子类 | Board | 板 |

| Geometry | 几何 | Assembly | 装配 |

| Cutout | 剪切 | Design | 设计 |

| Outline | 外框 | Dimension | 尺寸 |

| Silkscreen | 丝印 | Top | 顶层 |

| Bottom | 底层 | Etch [etʃ] | 刻蚀/线路层 |

| Manufacturing | 制造 | Nc Drill | 无连接的钻孔 |

| Package | 封装 | Pastemask | 助焊层/钢网层 |

| Bound | 边界 | Soldermask | 阻焊层 |

| Pin | 引脚 | Via | 过孔 |

| Keepin | 保持在...里面 | Keepout | 保持在...外面 |

| Ref Des | 位号,Reference Designator [ˈdezɪɡneɪtə(r)] | Route | 布线 |

调整快捷键设置

按照 alias 按键 命令 或者 funckey 按键 命令

的格式,修改 Cadence SPB 17.4 安装目录

D:\Software\Tech\Cadence\SPB_17.4\share\pcb\text 下的

env 配置文件,就可以调整 Allegro PCB

Editor 的快捷键设置,而 env

文件默认的快捷键配置如下面的表格所示:

| 快捷键 | 功能描述 | 快捷键 | 功能描述 |

|---|---|---|---|

| F2 | Zoom Fit | Shift + F2 | Property Edit |

| F3 | Add Connect | Shift + F3 | Slide |

| F4 | Show Element | Shift + F4 | Show Measure |

| F5 | Redraw | Shift + F5 | Copy |

| F6 | Done | Shift + F6 | Move |

| F7 | Next | Shift + F7 | Dehilight |

| F8 | Oops | Shift + F8 | Hilight Pick |

| F9 | Cancel | Shift + F9 | Vertex |

| F10 | Grid Toggle | Shift + F10 | Save_as Temp |

| F11 | Zoom In | Shift + F11 | Zoom Previous |

| F12 | Zoom Out | Shift + F12 | Zoom World |

| ~N | New | Ctrl + F2 | Next |

| ~O | Open | Ctrl + F5 | Color192 |

| ~S | Save | Ctrl + F6 | Layer Priority |

| ~D | Delete | Ctrl + Shift + F5 | Status |

| ~Z | Undo | + | subclass -+ |

| ~Y | Redo | - | subclass -- |

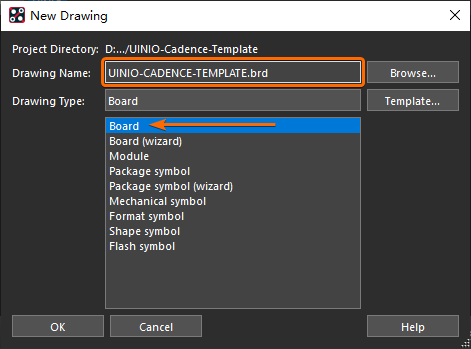

新建 .brd 版图工程

鼠标点击菜单栏上的【File -> New...】,选择弹出对话框中的

Drawing Type 类型为 Board,并且将

Drawing Name 名称设置为

UINIO-CADENCE-TEMPLATE.brd:

这样就完成了 UINIO-CADENCE-TEMPLATE.brd

版图文件的创建,此时的工程文件目录结构如下面所示:

1 | └─UINIO-Cadence-Template |

导入设计资源

如前所述,焊盘文件以及 PCB 封装,都会被保存在当前工程的相应目录下面,使用之前需要在 Allegro PCB Editor 当中指定这些目录:

devpath:存放第 3 方网表相关的 Device 文件,这些文件中记录有 PCB 封装的引脚信息,导入第三方网表时会与这些引脚信息进行比对。padpath:存放 PCB 封装相关的焊盘文件。psmpath:存放版图上的 PCB 封装文件。steppath:存放 PCB 封装所对应的 3D 模型。

鼠标点击 Allegro PCB Editor 菜单栏上的【Setup ->

User Preferences】,在弹出的对话框中选择【Path -> Library】项,主要对

devpath、padpath、psmpath、steppath

这四项进行设置:

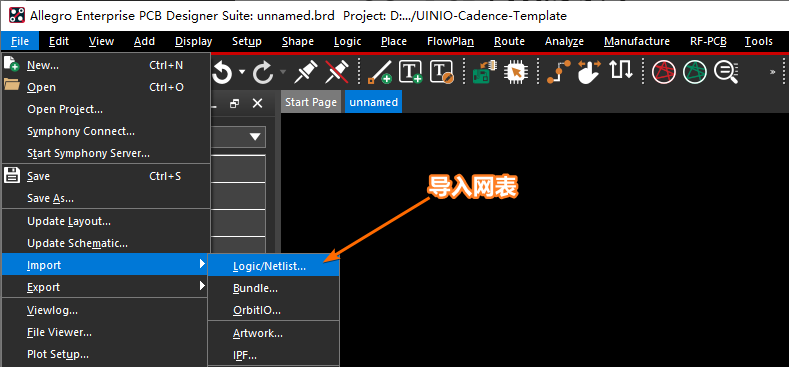

导入网表

当在 Allegro PCB Editor 新建了一个 .brd

后缀的 PCB 文件以后,就可以鼠标点击菜单栏上的【File -> Import ->

Logic/Netlis】进行网表的导入操作:

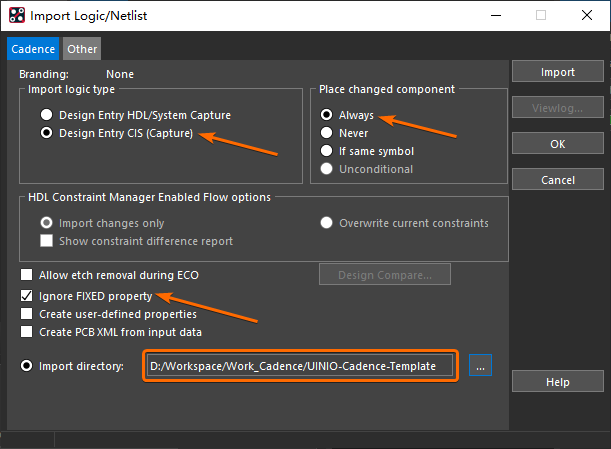

如果是 OrCAD Capture CIS 导出的网表,就在弹出对话框中,选择默认打开的【Cadence】选项卡,勾选如下设置的同时,指定网表文件的存放路径:

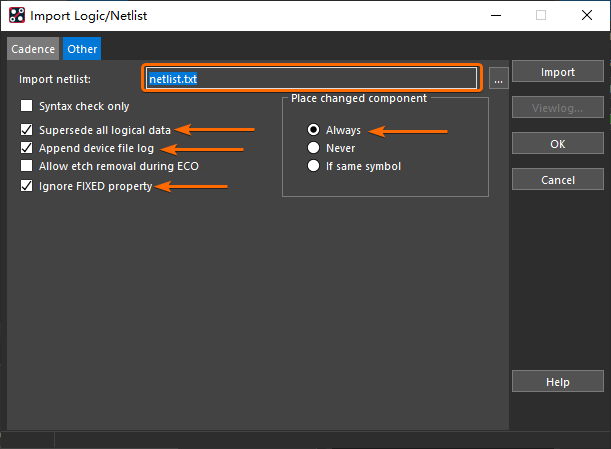

如果是第三方 EDA 工具导出的网表文件,则需要切换至【Other】选项卡,勾选如下的选项,并且指定第三方网表的保存路径:

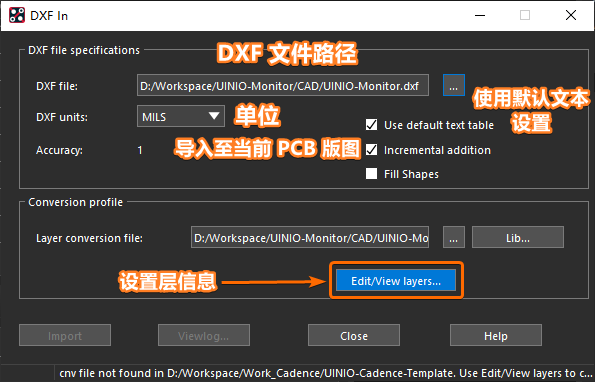

导入 PCB 板框

DWG 或者 DXF

格式的板框文件,由结构工程师借助专业的 CAD 工具绘制而成,鼠标依次点击

Allegro PCB Editor 菜单栏上的【File -> Import ->

DXF】,在弹出的对话话中进行如下设置:

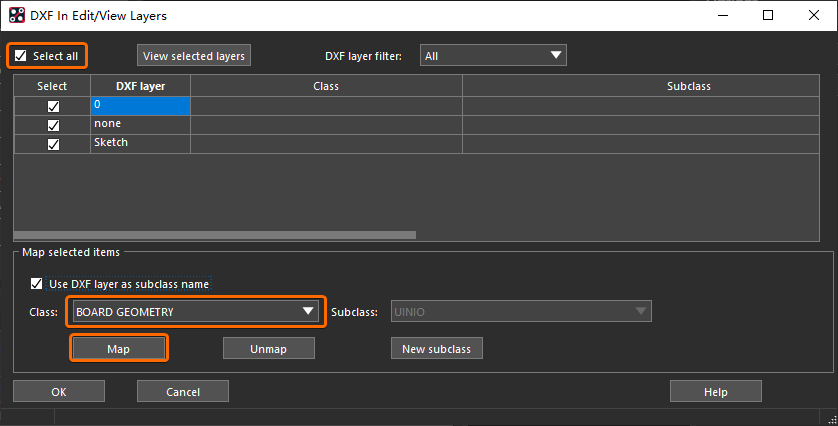

选择 DXF 文件所要导入的图层(通常选择

BOARD GEOMETRY),其它设置项可以参考下图进行修改,最后按下【Map】按钮将这里设置的

Class 和 Subclass 映射到 DXF 图层:

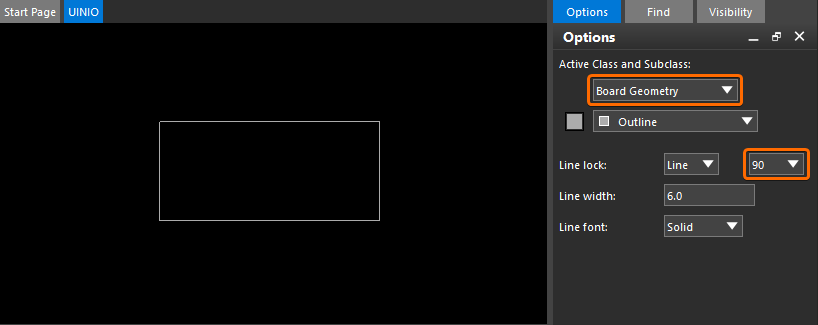

除此之外,Allegro PCB Editor 还支持自定义简单形状的 PCB 板框,鼠标点击菜单栏上的【Add -> Line】命令,就可以在 Board Geomertry 层(在右侧控制面板指定)绘制自定义的 PCB 板框:

层叠设置

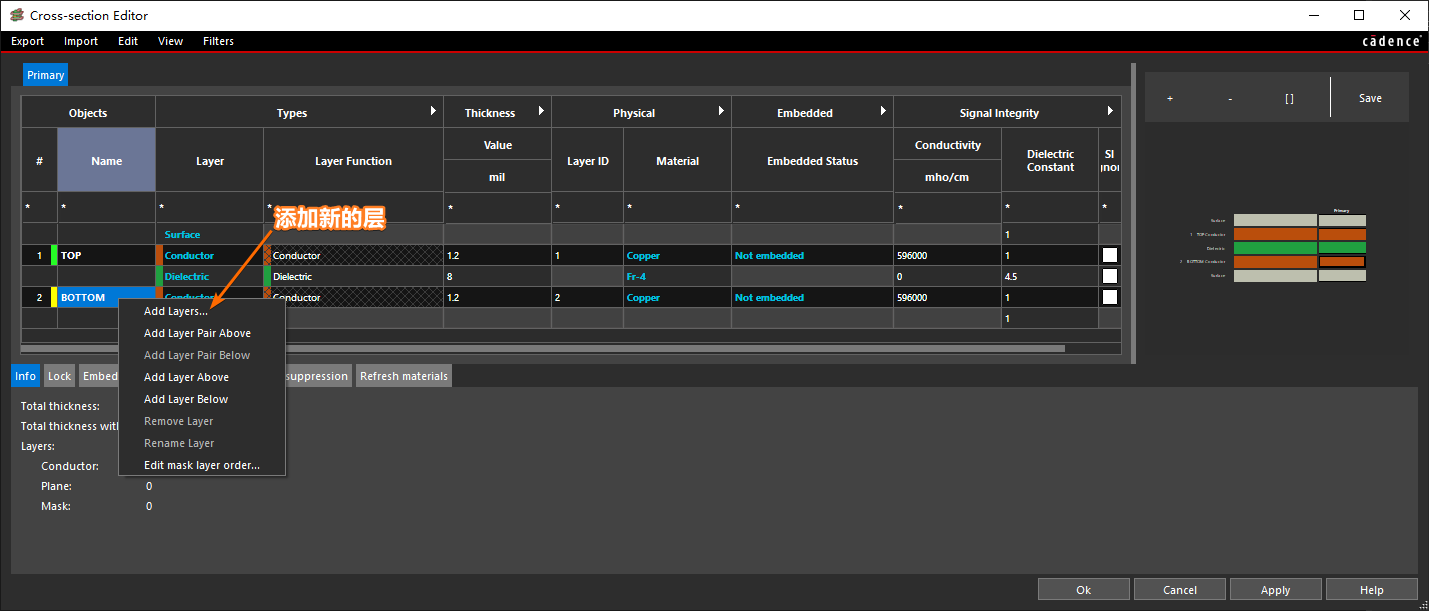

执行 Allegro PCB Editor 菜单栏上面的【Setup -> Cross Section】命令,就可以打开 PCB 叠层管理器:

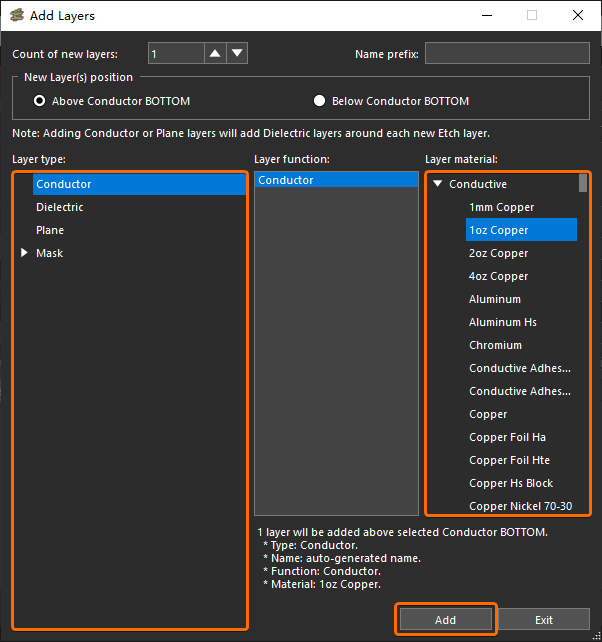

在叠层名称上展开鼠标右键菜单,单击上面的【Add

Layer】项,就可以添加新的 PCB

叠层(需要指定叠层的类型、功能、材料):

注意:Allegro PCB Editor 的叠层管理器当中,使用鼠标双击自定义叠层的名称,就可以对其执行修改操作。

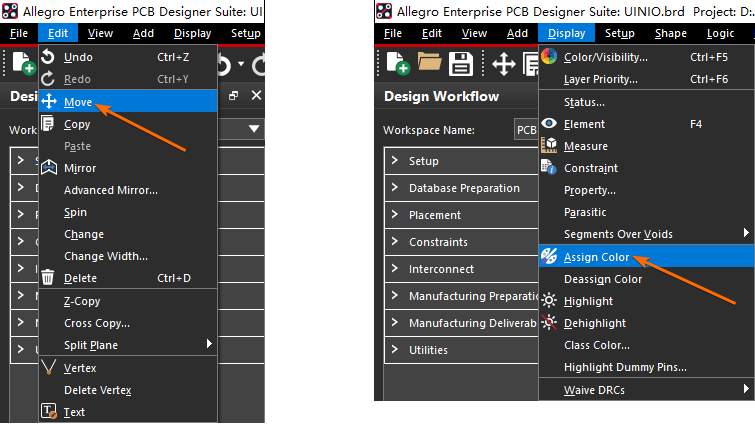

原理图 & PCB 交互模式

启用原理图与 PCB 的交互选择模式,需要鼠标点击 OrCAD Capture

CIS 菜单栏上的【Options ->

Preference】项,然后选择【Miscellaneous】选项卡,勾选

Enable Intertool Communication 启用交互模式:

在导入 Cadence SPB 网表之后,首先需要在 Allegro PCB Editor 中执行【Move】命令,选中 PCB 版图上的元件(下图左)。然后选择菜单栏上的【Display -> Assign Color】,高亮 PCB 版图上被选中的元件,此时原理图当中对应的元件就会自动被选中:

常用 PCB 版图布局操作

Allegro PCB Editor 当中进行元素布局的时候,需要先执行菜单栏上的命令,再框选需要执行操作的元素,这是与其它 EDA 工具使用习惯上的一个重大区别:

| PCB 版图布局操作 | 操作方式 |

|---|---|

| 移动元素 | 点击菜单栏【Edit -> Move】。 |

| 旋转元素 | 点击菜单栏【Edit -> Spin】。 |

| 镜像元素 | 点击菜单栏【Edit -> Mirror】。 |

| 复制元素 | 点击菜单栏【Edit -> Copy】。 |

| 测量距离 | 点击菜单栏【Display -> Measure】。 |

| 高亮网络 | 点击菜单栏【Display -> Highlight】。 |

| 取消高亮网络 | 点击菜单栏【Display -> Dehighlight】。 |

| 分配网络颜色 | 点击菜单栏【Display -> Assign Color】。 |

| 显示元素信息 | 点击菜单栏【Display -> Element】,然后选中要查看信息的元素。 |

| 互换元素位置 | 点击菜单栏【Place -> Swap -> Components】。 |

| PCB 版图布局组合操作 | 操作方式 |

|---|---|

| 对齐元素 | 首先点击菜单栏【Setup -> Application Mode -> Placement Edit】,然后框选分组元素,点击鼠标右键菜单上的【Align components】项。 |

| 分组元素 | 首先点击菜单栏【Setup -> Application Mode -> Placement Edit】,然后框选分组元素,点击鼠标右键菜单上的【Place replicate create】项。 |

| 临时分组元素 | 首先点击菜单栏【Edit -> Move】,然后框选需要临时分组的元素,点击鼠标右键菜单上的【Temp Group】项。 |

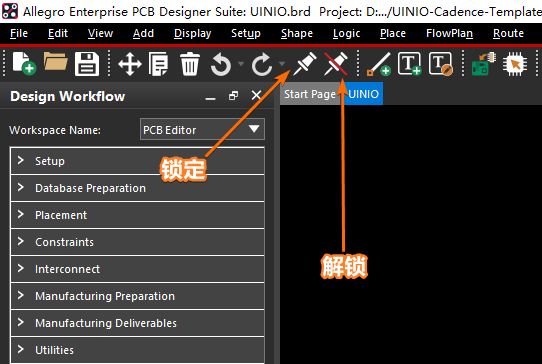

元素的锁定与解锁

使用 Allegro PCB Editor 进行元件布局操作的时候,由于一些结构件和定位孔的位置固定,为了防止后期误操作,通常会使用锁定命令将其锁定。使用时需要鼠标先点击工具栏上的【Fix】和【Unfix】图标,然后再选择需要锁定或者解锁的元素:

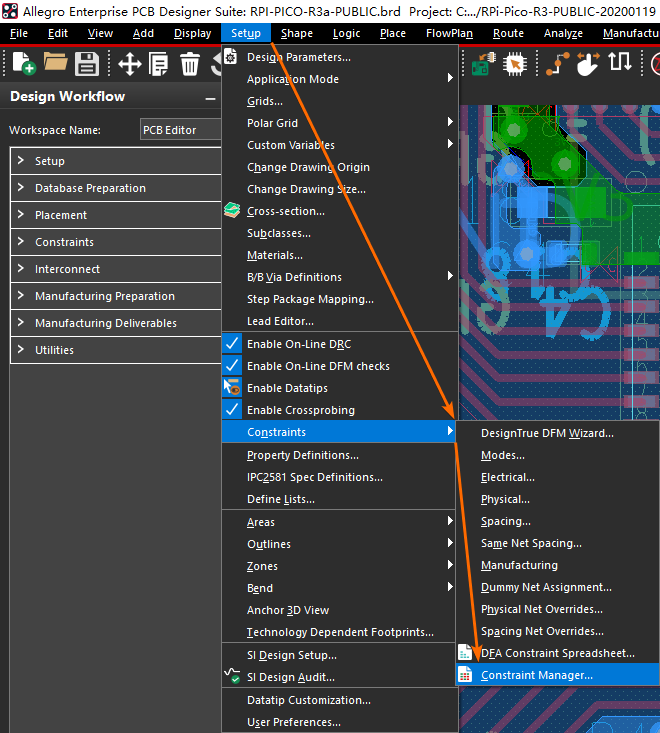

善用约束管理器

网络类(Net

Class)用于将具备同一属性的电路网络放置在一起,分类的目的在于可以使用统一的规则对布线进行约束和管理。例如

GND 和 Power

网络放置在一起构成电源网络类,或者将 90Ω

的 USB 差分信号放置在一起构成 90Ω

差分类。鼠标选择 Allegro PCB Editor

菜单栏上面的【Setup -> Constraints -> Constraint Manager...】项

:

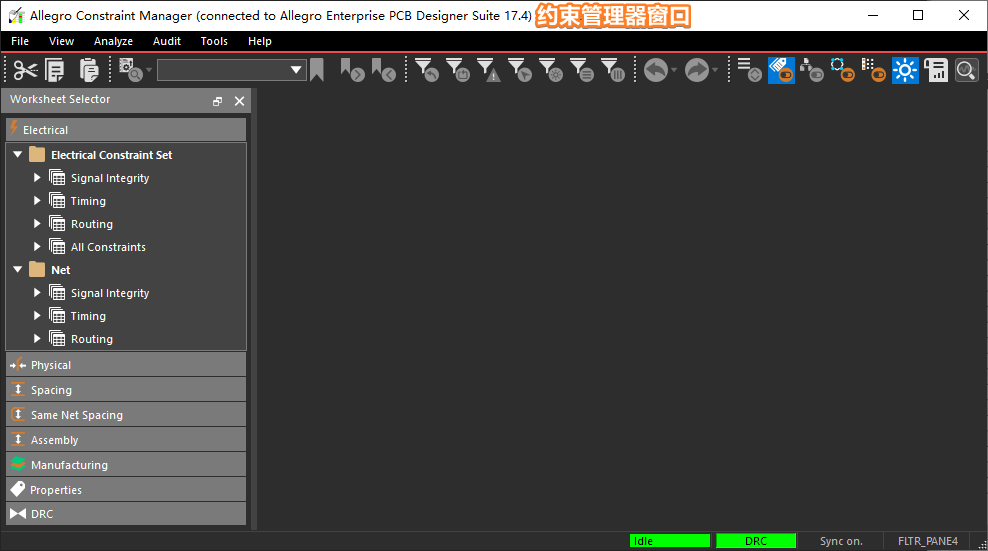

就可以打开 Allegro PCB Editor 提供的约束管理器窗口:

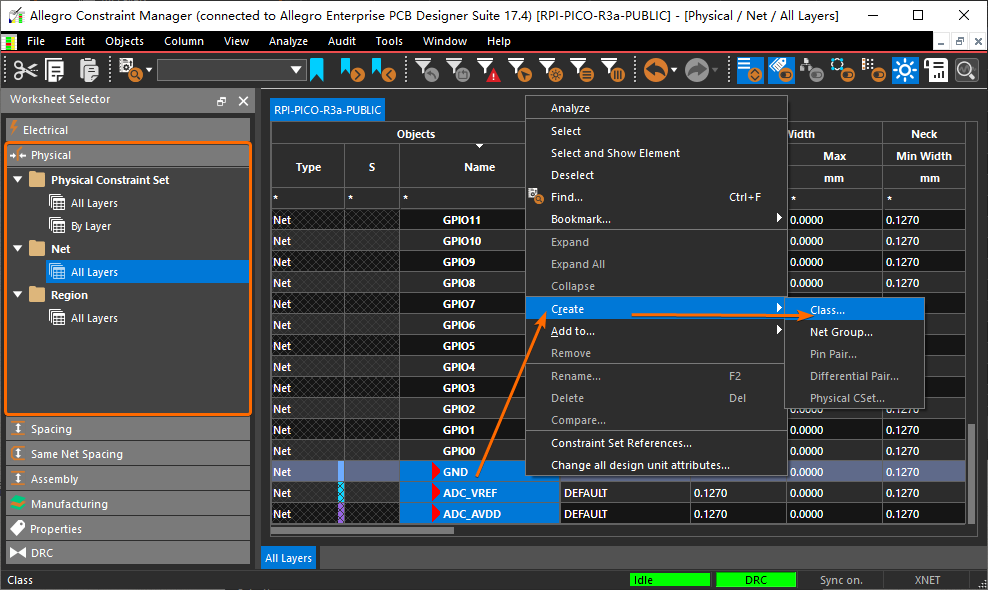

创建 Class 网络类

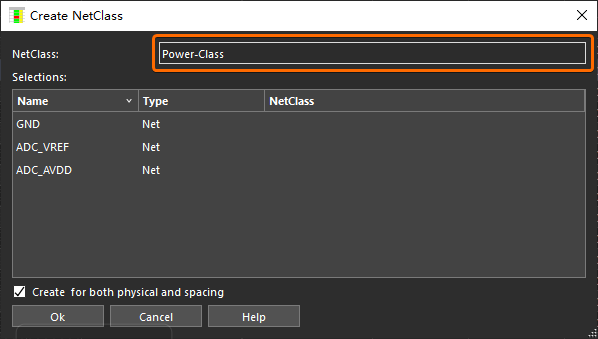

网络类 Class 通常用于依照功能模块对电路网络进行分类,鼠标依次选择 约束管理器窗口 左侧的【Physical -> Net】菜单项,然后使用【Ctrl/Shift + 鼠标左键】选中多个网络,再点击鼠标右键菜单中的【Create -> Class...】创建 Class 网络类:

在随后弹出的网络类窗口当中,对创建的 Class 网络类进行命名,然后鼠标点击【确定】按钮即可:

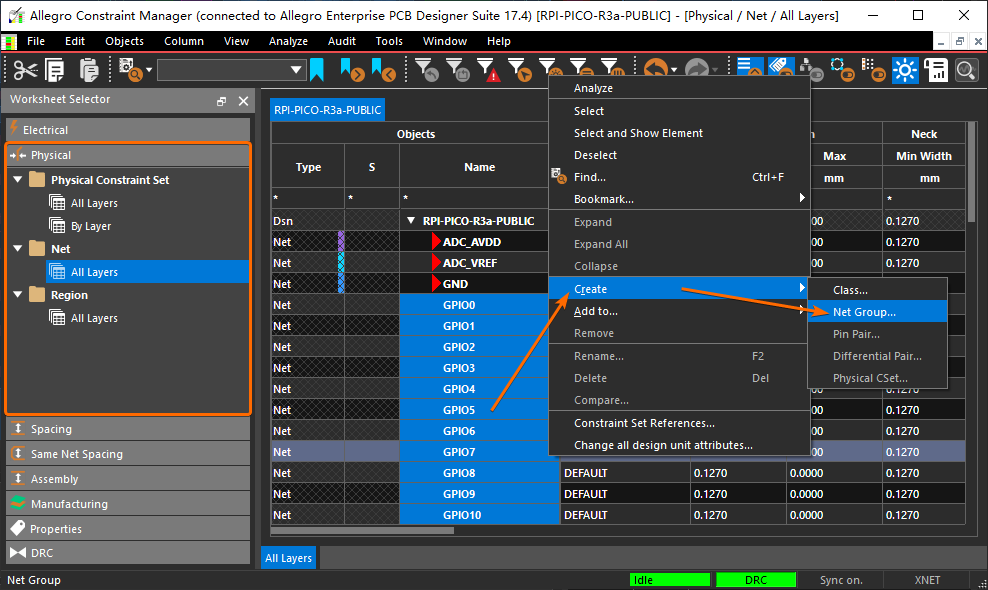

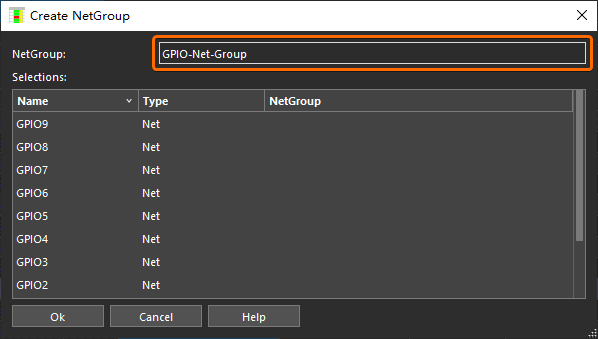

创建 Net Group 网络分组

网络分组 Net Group

用于对某一类型的信号进行分组,例如 DDR 颗粒的同一组 D0~D7

数据线就可以创建为一组 Net Group。其创建步骤与网络类 Class

相似,不同之处在于点击的是鼠标右键菜单上的【Create -> Net

Group...】项:

在随后弹出的网络类窗口当中,对要创建的网络分组 Net Group 进行命名,然后鼠标点击【确定】按钮即可:

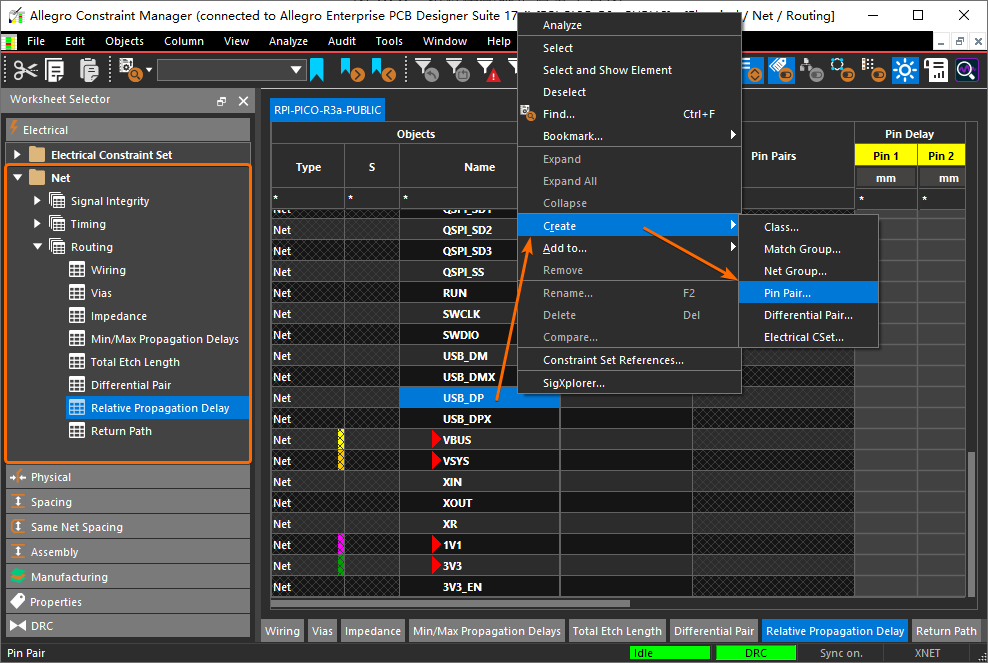

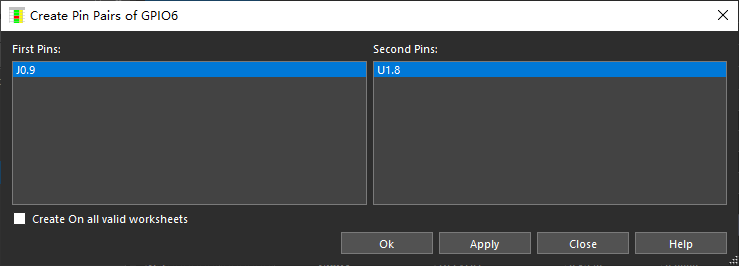

创建 Pin Pair 引脚配对

引脚配对 Pin Pair 通常用于等长布线操作,选择 约束管理器窗口 左侧的【Electrical -> Net -> Routing -> Relative Propagation Delay】菜单项,然后选中一条需要实现等长的信号线,再点击鼠标右键菜单上的【Create -> Pin Pair...】创建引脚配对:

执行上述操作之后,弹出的对话框中会显示该信号线所连接的全部引脚,如果是点对点可以直接按下【OK】按钮,如果该信号线上存在着多个连接点,则选择需要进行等长操作的两个连接点即可:

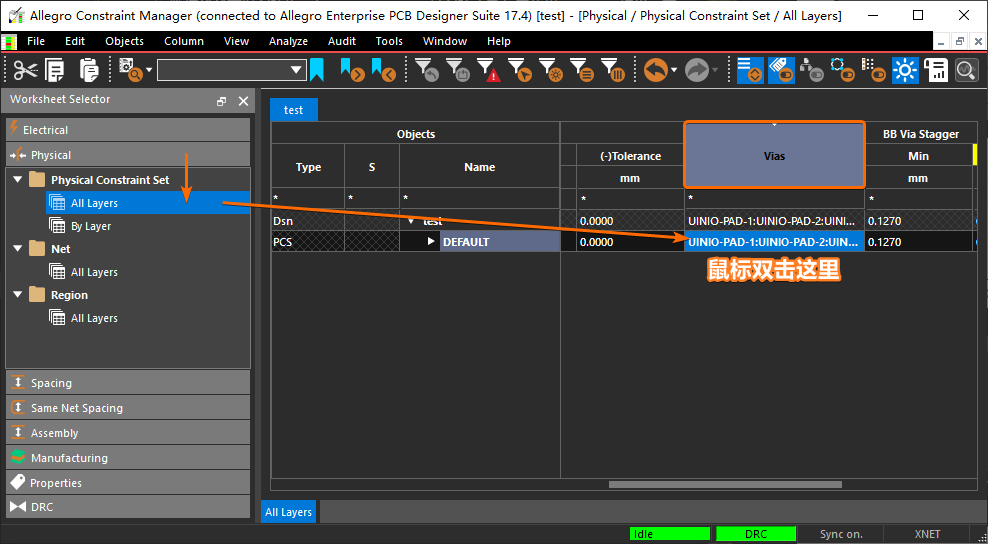

添加过孔约束

选择 约束管理器窗口 左侧的【Physical -> Physical

Constraint Set -> All Layers】菜单项,鼠标双击右侧表格当中

Vias 栏下面的空白项目:

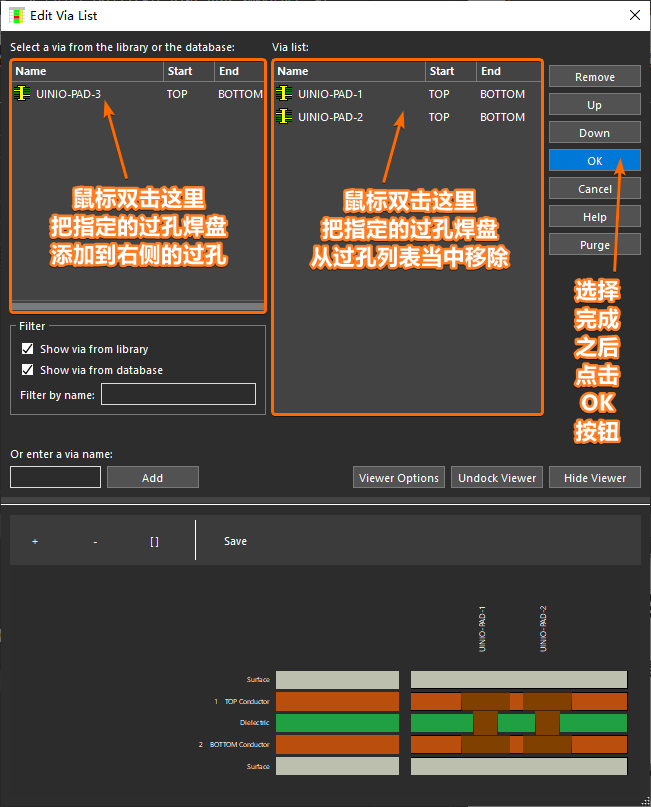

在弹出的 Edit Via List 对话框当中,使用鼠标双击左侧待选的过孔,就可以将其添加至右侧的 PCB 过孔列表当中,操作完成之后点击【OK】按钮。接下来就可以在 PCB 布线过程当中,双击鼠标左键实现打孔换层的操作:

开始执行铺铜操作

选择铺铜区域

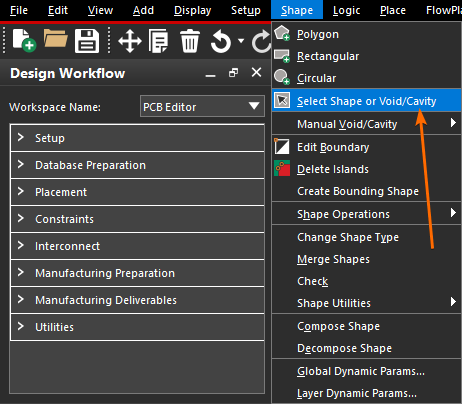

鼠标点击 Allegro PCB Editor 菜单栏上的 【Shape -> Select Shape or Void/Cavity】,就可以选中 PCB 版图上已经铺铜的区域,该操作是其它一切铺铜相关操作的基础,因而务必熟练掌握:

修改铺铜区域属性

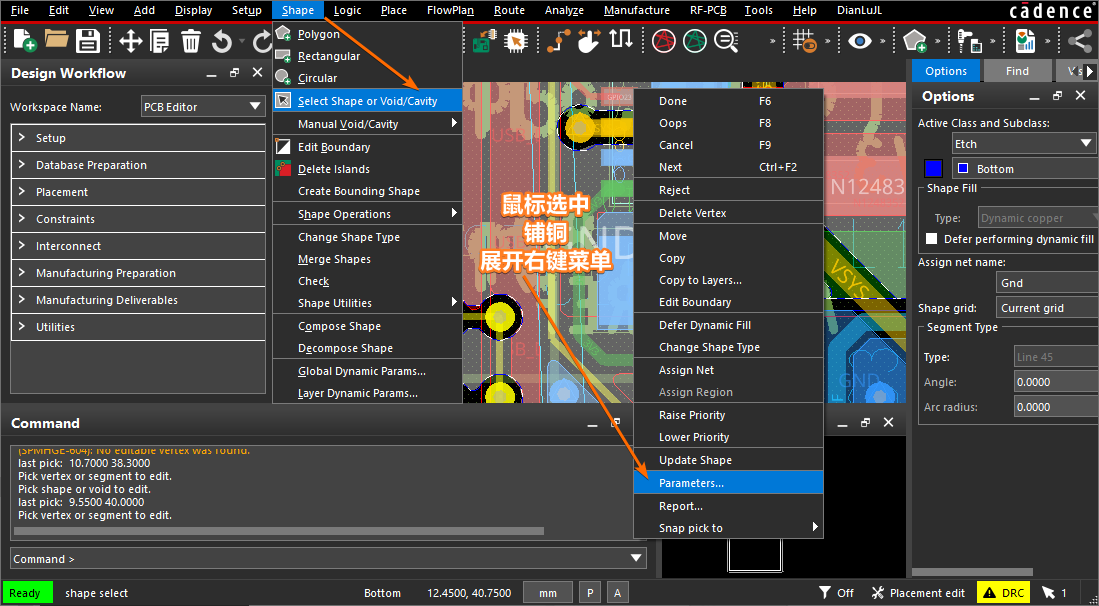

首先点击 Allegro PCB Editor 菜单栏上的 【Shape -> Select Shape or Void/Cavity】选中 PCB 上已经铺铜的区域,然后选中鼠标右键菜单上的【Parameters】选项,在打开的对话框里就可以调整该铺铜区域的各项属性:

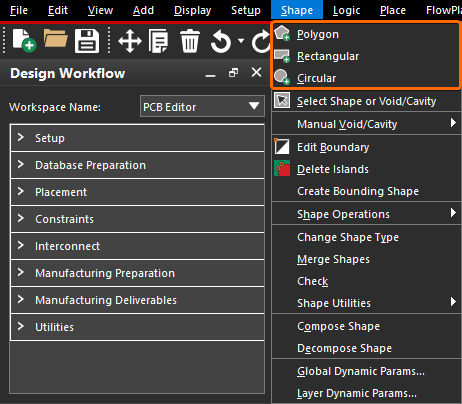

手动铺铜

执行 Allegro PCB Editor 菜单栏上的【Shape ->

Polygon/Rectangular/Circular】项,就可以手动绘制出多边形、矩形、圆形的铺铜区域:

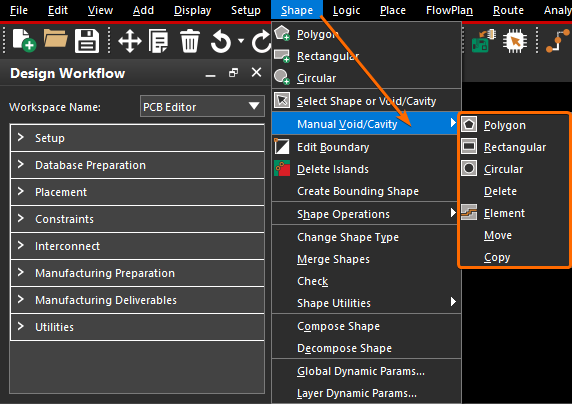

手动挖铜

挖铜就是移除多余的铺铜区域,执行 Allegro PCB Editor 菜单栏上的【Shape -> Manual Void/Cavity】项,就可以展开下图中的一系列挖铜命令:

自动移除孤铜

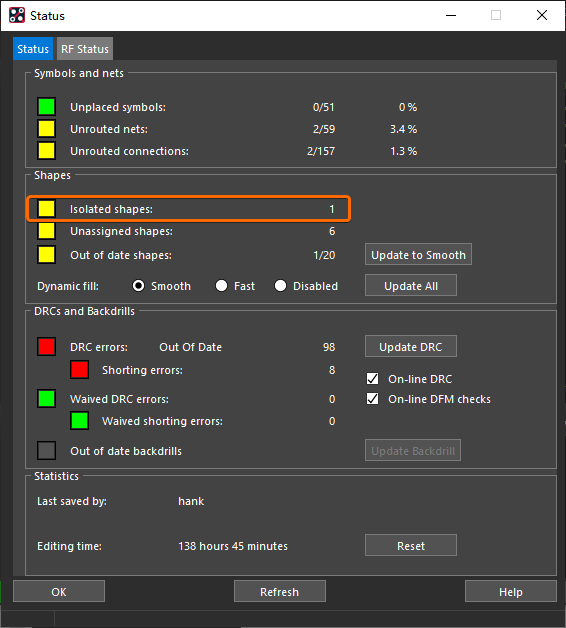

孤铜是指在 PCB 中孤立无连接的覆铜区域,通常需要对其进行删除处理。首先执行 Allegro PCB Editor 菜单栏上的【Display -> Status】命令,查看当前 PCB 版图当中是否存在有孤铜区域:

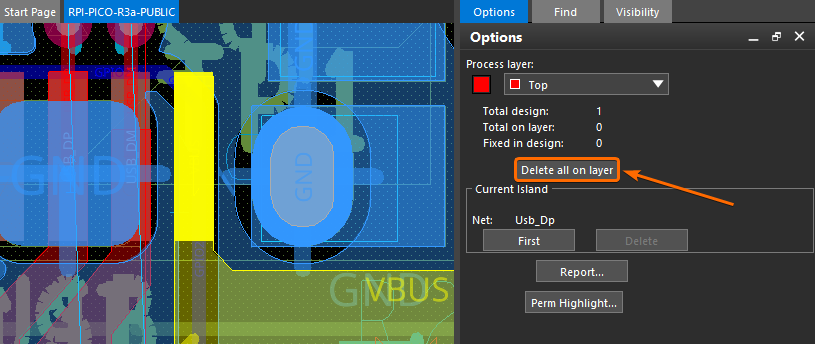

如果存在有孤铜区域(上图黄色框选部分),那么首先需要执行菜单栏上的【Shape -> Delete Island】命令,然后在 Allegro PCB Editor 右侧控制面板上的【Options】选项卡下面,点击【Delete all on layer】按钮删除这些孤铜区域:

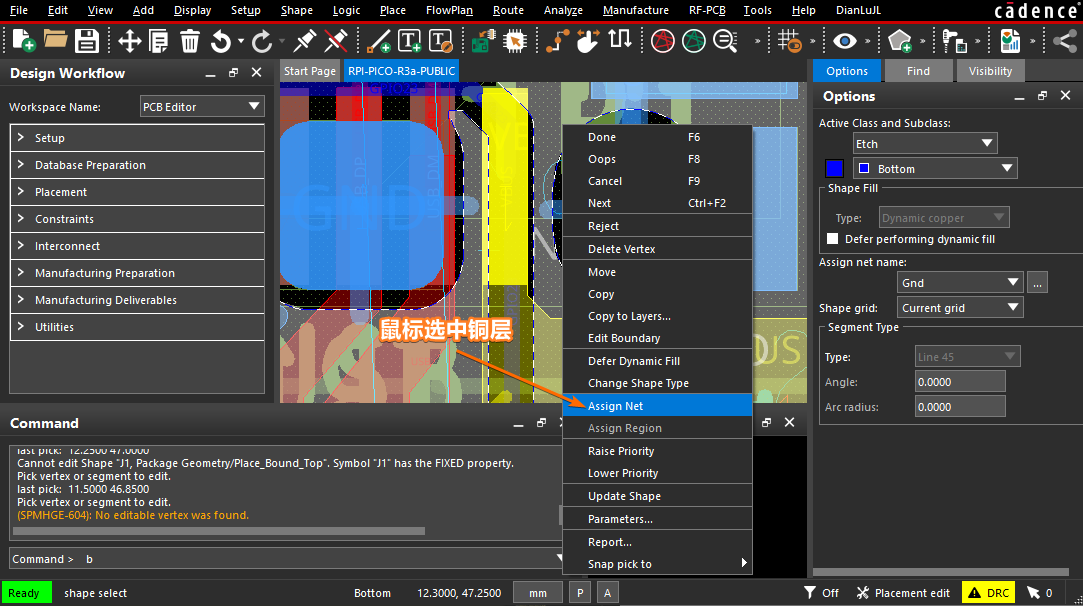

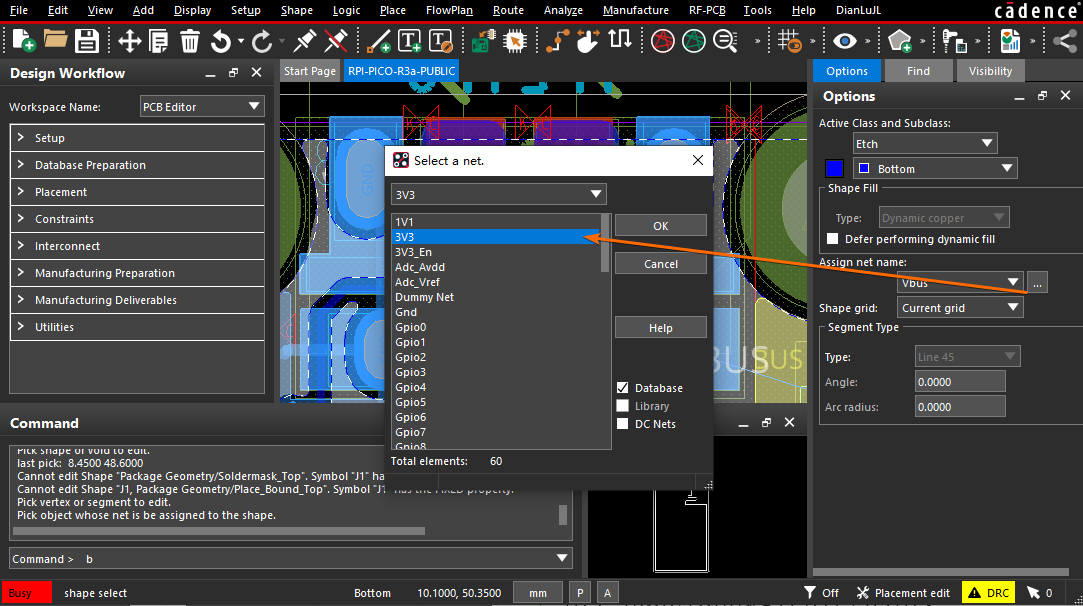

调整铺铜网络

调整铺铜的电路网络,首先需要执行菜单栏上的【Shape -> Select Shape or Void/Cavity】命令,选择需要分配或调整网络的铺铜区域,然后点击鼠标右键菜单上的【Assign Net】菜单项:

最后,就可以在 Allegro PCB Editor 右侧控制面板上的【Options】选项卡里,点击【...】按钮进行电路网络的分配:

静/动态铺铜转换

动态铺铜(Dynamic Shape)可以自动避让元件和过孔,而静态铺铜(Static Shape)则需要手动进行避让,PCB 版图设计的时候两者可以相互进行转换。

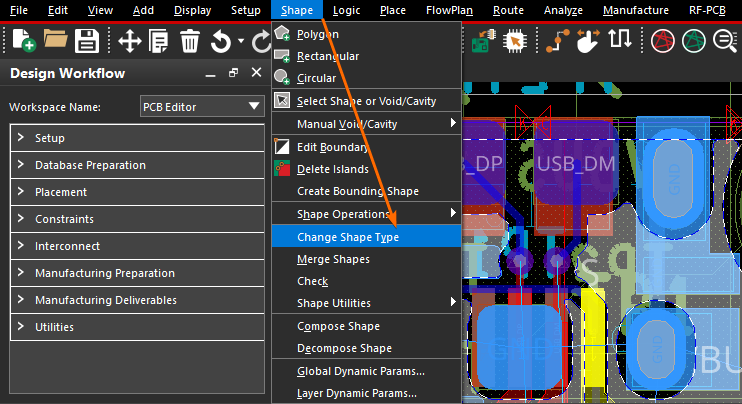

首先,依然需要执行菜单栏上的【Shape -> Select Shape or Void/Cavity】命令,选中需要进行转换的铺铜区域,然后点击鼠标右键菜单上的【Change Shape Type】选项,就转换铺铜区域的静态与动态属性:

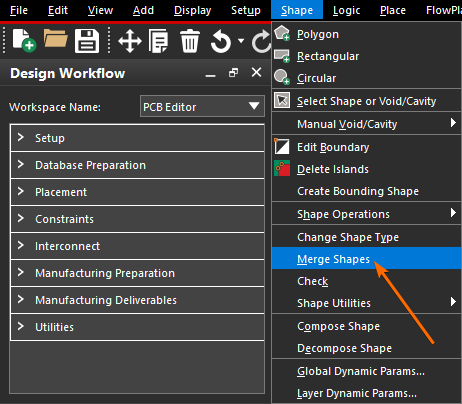

合并铺铜区域

Allegro PCB Editor 支持将两个处于相同网络的铺铜区域进行合并,或者将一个没有指定网络的铺铜区域,与一个指定了网络的铺铜区域进行合并。首先选中需要进行合并操作的覆铜区域,然后执行菜单栏上的【Shape -> Merge Shapes】命令即可:

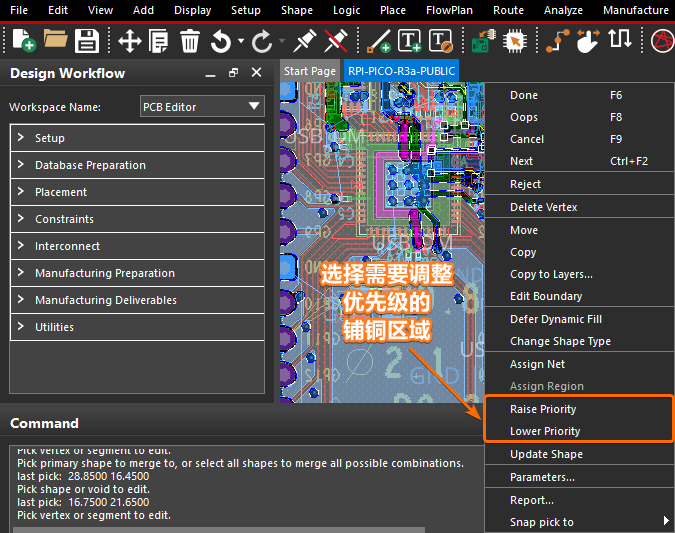

铺铜优级级

如果铺铜区域出现重叠的情况,则可以让其中一个铺铜区域的优先级,高于另外一个铺铜区域,此时后者将会自动避让重叠的部分。

这里同样通过菜单栏上的【Shape -> Select Shape or Void/Cavity】命令,选中需要提高或者降低优先级的铺铜区域,然后点击鼠标右键菜单上的【Raise Priority】或者【Lower Priority】选项,就可以提高或者降低该铺铜区域的优先级。

分隔平面铺铜

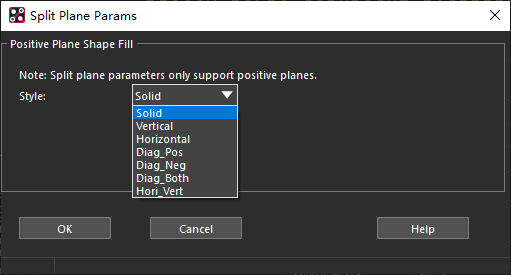

首先,执行 Allegro PCB Editor 菜单栏上的【Edit ->

Split Plane ->

Parameters】,设置分隔平面(即需要自动铺铜的层)的参数(通常选择

Solid 实心铺铜):

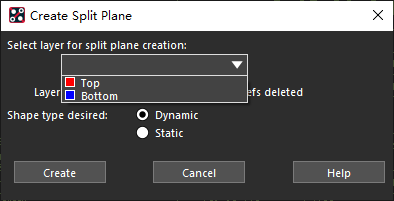

然后,再执行菜单栏上的【Edit -> Split Plane -> Create】建立分隔平面命令,选择需要进行自动铺铜操作的层:

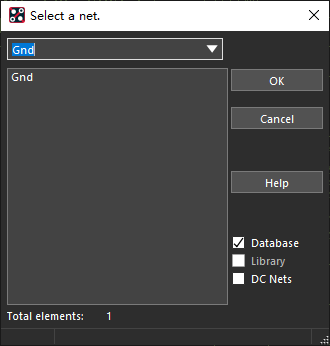

最后,在弹出的窗口里,选择当前需要自动铺铜的电路网络,完成之后鼠标点击【OK】按钮,Allegro PCB Editor 就会自动对该层电路网络进行铺铜:

铺铜操作总结

| 铺铜选择操作 | 操作说明 |

|---|---|

| 选择铺铜区域 | 点击菜单栏上的【Shape -> Select Shape or Void/Cavity】选项,然后再在 PCB 版图上执行选择操作。 |

| 其它铺铜操作 | 操作说明 |

|---|---|

| 手动铺铜 | 直接点击菜单栏上的【Shape -> Polygon/Rectangular/Circular】选项。 |

| 手动挖铜 | 直接点击菜单栏上的【Shape -> Manual Void/Cavity】选项。 |

| 自动移除孤铜 | 直接点击菜单栏上的【Shape -> Delete Island】选项。 |

| 合并铺铜区域 | 选中铺铜区域之后,执行菜单栏上的【Shape -> Merge Shapes】选项。 |

| 修改铺铜区属性 | 选中铺铜区域之后,点击鼠标右键菜单上的【Parameters】选项。 |

| 调整铺铜网络 | 选中铺铜区域之后,点击鼠标右键菜单上的【Assign Net】选项。 |

| 动静态铺铜转换 | 选中铺铜区域之后,点击鼠标右键菜单上的【Change Shape Type】选项。 |

| 铺铜优级级 | 选中铺铜区域之后,点击鼠标右键菜单上的【Raise Priority】或者【Lower Priority】选项。 |

| 自动对层铺铜 | 首先点击菜单栏【Edit -> Split Plane -> Parameters】设置铺铜方式,然后点击【Edit -> Split Plane -> Create】选择铺铜的层,最后指定当前自动铺铜的网络。 |

常用的布线操作

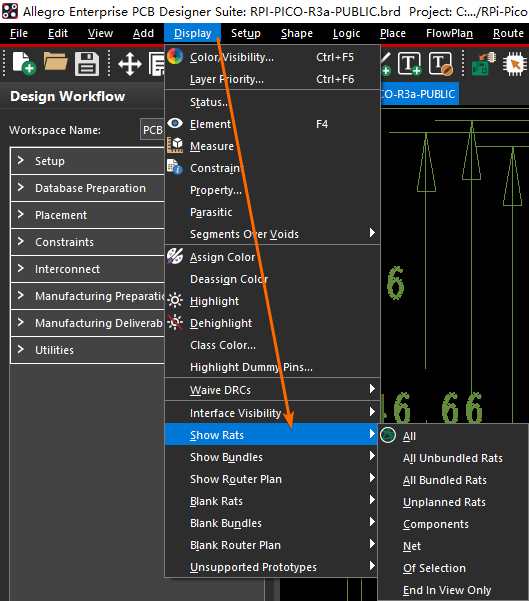

显示飞线

执行 Allegro PCB Editor 菜单栏上的【Display ->

Show Rats/Blank Rats】可以显示或者隐藏 PCB

版图上各个元件的原理图飞线连接关系,在弹出的下拉菜单里存在有

All(显示/隐藏所有的飞线)、Net(显示/隐藏指定网络的飞线)、Components(显示/隐藏所选择的元器件的飞线)三个选项:

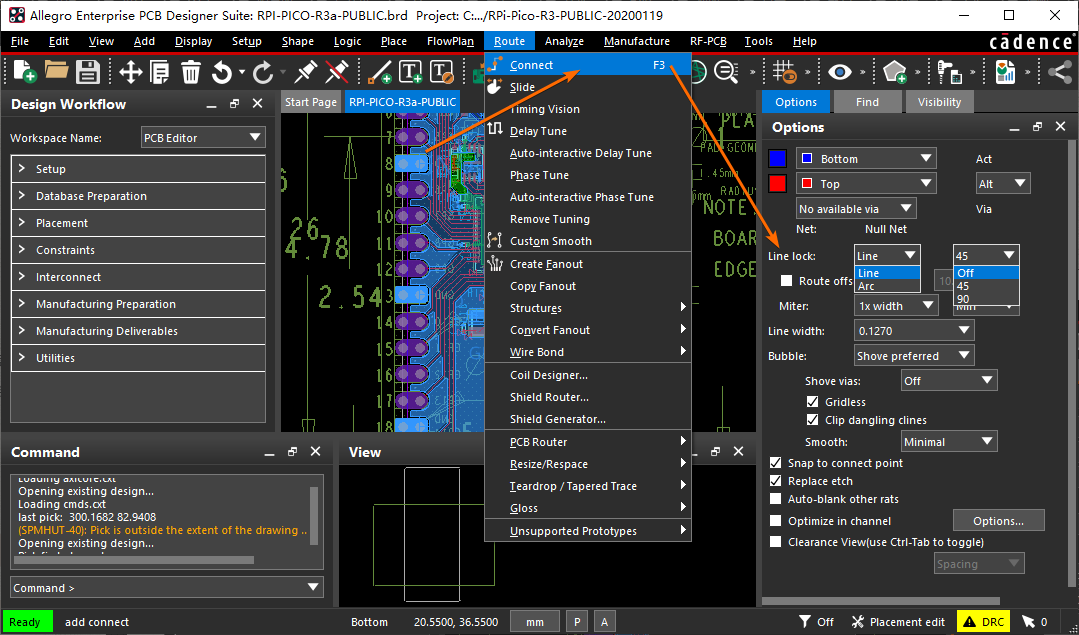

调整布线形态

在布线过程当中,经常需要调整走线的形状以及弯折的角度,此时可以执行

Allegro PCB Editor 菜单栏上的【Route ->

Connect】命令,将【Options】面板中的 Line Lock 修改为

Line/Arc(走线形状)以及

Off/45/90(走线弯折角度):

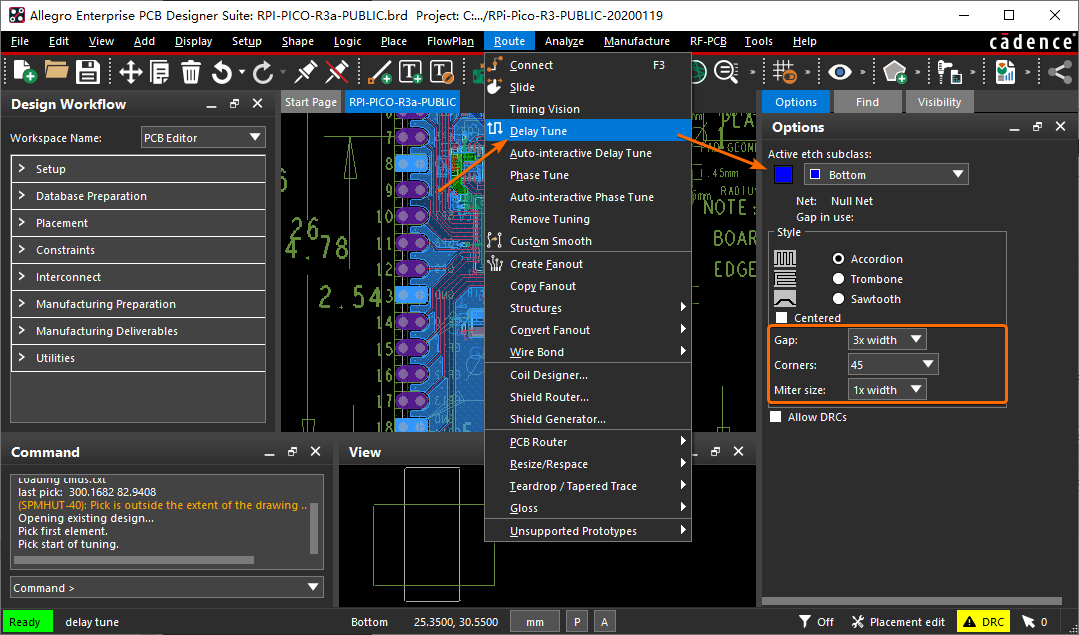

蛇形走线

PCB 进行等长设计时,经常会使用到蛇形走线。首先执行菜单栏上的【Route -> Delay Tune】命令,然后就可以通过右侧的【Options】面板,配置蛇形布线的相关参数:

注意:【Options】面板中的

Style参数用于设置蛇形走线的样式,而【Gap】通常被设置为 3 倍线宽,Corners通常设置为45°,最小拐角长度Miter Size通常设置为 1 倍线宽。

写给有经验 PCB 工程师的 Cadence SPB 17.4 极速上手指南