内置集成电路总线协议 I²C 简明指南

内置集成电路总线(Inter-Integrated

Circuit)是一种串行通信协议,其英文缩写为

I²C,因为中间存在 2 个英文字母

I,所以被读作 I Square C,中文读作

I 平方 C 或者 I 方 C

总线。本文后续内容为了书写方便,会将 I²C 简写为

I2C。该总线协议需要串行数据线(SDA,Serial

Data)和串行时钟线(SCL,Serial

Clock)两条信号线,接线方式较为简单,通常用于连接微控制器、存储器、传感器等低速元器件。

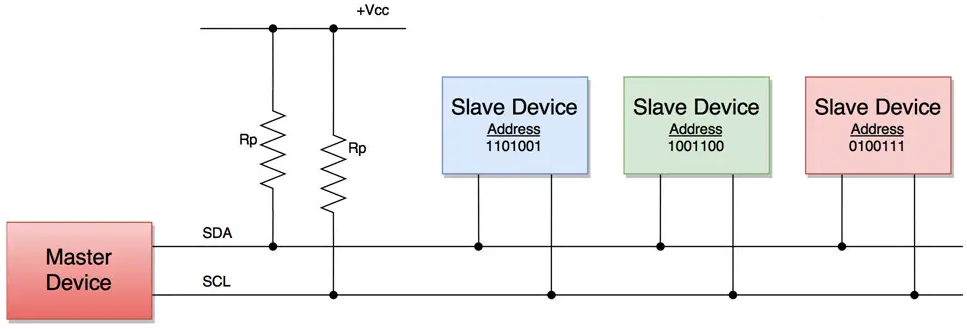

在 I²C

总线通信协议当中,规定总线上可以存在一个主设备以及多个从设备。主设备掌控着整个通信过程,负责发起、控制、停止通信。而从设备则需要等待主设备请求、接收、发送数据。主设备与从设备之间的数据交换采用特定的数据帧格式,每个数据帧包含有

地址、数据、控制

信息。主设备会根据从设备的 I2C

地址来选择总线上需要进行通信的外设,从设备则根据控制信息返回相应的响应。

演进历程

1982

年荷兰飞利浦(Philips)公司为自家的芯片产品制订了 I²C

总线技术规范,原始规范只能提供 100kHz 的通信速率,以及 7

位的地址空间(由于存在有保留地址,总线上设备数量被限制为 112

个)。后续在 1992 年发布了第一个公共规范,增加了

400kHz 快速模式,以及扩展的 10

位地址空间。经过多年的发展,目前 I2C

协议规范已经能够提供下面表格当中的五种工作速率模式:

| I2C 总线模式 | 英文名称 | 典型传输速率 |

|---|---|---|

| 标准模式 | Standard Mode | 100 KHz |

| 快速模式 | Fast Mode | 400 KHz |

| 增强快速模式 | Fast Mode Plus | 1 MHz |

| 高速模式 | High-Speed Mode | 3.4 MHz |

| 极速模式 | Ultra-Fast Mode | 5 MHz |

注意:英特尔(Intel)公司于 1995 年推出的系统管理总线(SMBus,System Management Bus)是一种基于 I2C 总线演变而来的变体,其提供了更加严格的控制模式,传输速率被限制在

10kHz ~ 100kHz范围之间,并且支持时钟超时、固定逻辑电平(I2C 的逻辑电平由总线上拉电阻连接的VCC决定)等特性。

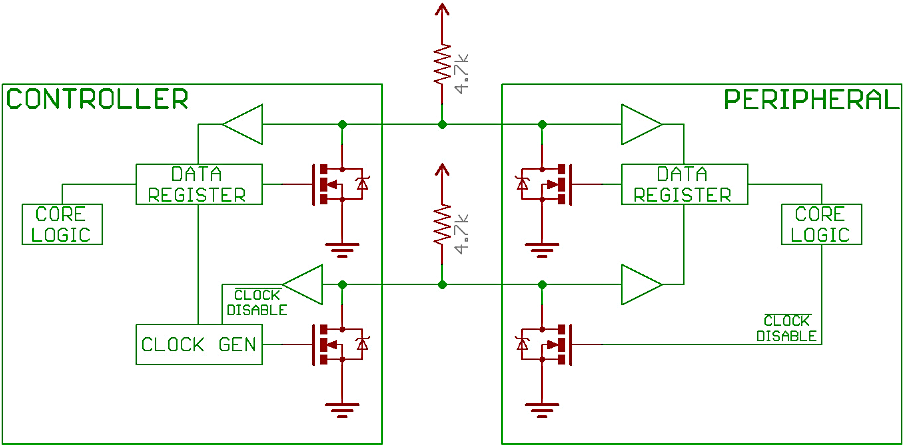

漏极开路设计

芯片内置的 I2C 总线驱动器,通常采用漏极开路设计(不同于 UART 和 SPI 总线),这意味着其可以将总线信号线拉低,但不能将总线信号驱动为高电平。从而在一个设备试图将 I2C 总线驱动为高电平,而另外一个设备又试图将总线电平拉低的时候,不会出现争抢总线资源的情况,从而避免损坏芯片内部的 I2C 总线驱动器,以及随之带来的功耗过大问题。正是因为如此,I2C 总线的信号线上都会存在一个上拉电阻 ,用于协助总线恢复到高电平状态。

注意:I2C 上拉电阻的选型需要根据总线上的主从设备进行选型(后续的内容会给出理论指导),但一个好的经验法则是从

4.7kΩ电阻开始,然后逐步向下进行调整。

探究上拉电阻的取值

上拉电阻的推导

I2C 总线是一种采用了漏极开路(Open-Drain)或者集电极开路(Open-Collector)的通信标准,因而可以支持具有不同工作电压的芯片和传感器相互通信。如下图所示,当总线没有被芯片引脚内部的漏极开路下拉为低电平时,I2C 总线的上拉电阻就会将总线电平进行拉高:

芯片 I2C 引脚内部的输入缓冲器,所能够读取的最小有效低电平 \(V_{OL}\) 决定了上拉电阻最小值 \(R_{P_{min}}\):

\[ R_{P_{min}} = \frac{V_{CC} - V_{OL_{max}}}{I_{OL}} \]

上拉电阻最大值 $R_{P_{min}} $ 受限于 I2C 总线的等效电容 \(C_B\),I2C 总线规范当中定义了信号的上升时间(Rise Time),如果上拉电阻的取值过大,可能会导致 I2C 总线在被下拉之前,没有足够的时间上升到有效的逻辑高电平。从时间 \(t=0\) 开始,RC 电路对振幅为 VCC 的电压阶跃响应,可以使用 RC 时间常数进行表示,因此 I2C 总线上的电压波形可以表达为下面的方程:

\[ V(t) = V_{CC} \times \bigg( 1 - e^{\frac{-t}{R_P \times C_B}} \bigg) \]

注意:RC 时间常数 \(\tau\) 是指电阻值 \(R\) 与电容值 \(C\) 的乘积,其单位为秒,表达的是电容器通过电阻器进行充电与放电的时间特性。

通常情况下,I2C 总线上的输入高电平电压(Input High Voltage)\(V_{IH}\)、输入低电平电压(Input Low Voltage)\(V_{IL}\) 与上拉参考电压 \(V_{CC}\) 之间的关系可以表达为如下的方程组:

\[ \begin{cases} V_{IH} = 0.7 \times V_{CC} = V_{CC} \times \big(1 - e^{\frac{-t_1}{R_P \times C_B}} \big) \\ V_{IL} = 0.3 \times V_{CC} = V_{CC} \times \big(1 - e^{\frac{-t_2}{R_P \times C_B}} \big) \end{cases} \]

基于上述方程组,可以将 I2C 总线信号的上升时间 \(t_R\) 描述为下面的公式:

\[ t_R = t_2 - t_1 = 0.8473 \times R_P \times C_B \]

由此,就可以推导出上拉电阻最大值 \(R_{P_{max}}\) 与上升时间 \(t_R\) 之间的函数关系:

\[ R_{P_{max}} = \frac{t_R}{0.8473 \times C_B} \]

推导出上拉电阻的最小值 \(R_{P_{min}}\) 与最大值 \(R_{P_{max}}\) 之后,就可以根据预定的传输速率和功率进行恰当的取值,较小的阻值可以带来更快的响应速度,较大的阻值则会带来更少的功率耗散。

I2C 总线规范参数

I2C 总线协议规范当中,对于前面内容提到的 \(t_R\)、\(C_B\)、\(V_{OL}\) 参数作出了如下定义:

| 参数名称 | 描述 | 标准模式(最大) | 快速模式(最大) | 增强快速模式(最大) |

|---|---|---|---|---|

| \(t_R\) | SDA 和 SCL 信号的上升时间 | 1000 ns |

300 ns |

120 ns |

| \(C_B\) | I2C 传输线等效电容 | 400 pF |

400 pF |

550 pF |

| \(V_{OL}\) | 低电平输出电压(3mA 电流源,\(V_{CC} > 2V\)) |

0.4 V |

0.4 V |

0.4 V |

低电平输出电压(2mA 电流源,\(V_{CC} \leq 2V\)) |

- | \(0.2 \times V_{CC}\) | \(0.2 \times V_{CC}\) |

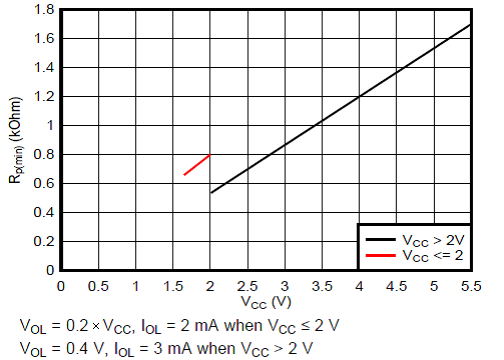

下面图像表达了 I2C 总线在标准模式和快速模式下,上拉电阻最小值 \(R_{P_{min}}\) 与上拉参考电压 \(V_{CC}\) 之间的关系:

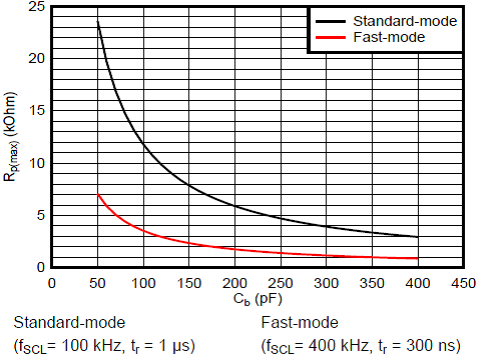

下面图像表达了 I2C 总线在标准模式和快速模式下,上拉电阻最大值 \(R_{P_{max}}\) 与上拉参考电压 \(V_{CC}\) 之间的关系:

上拉电阻计算实例

当一个 I2C 总线处于快速模式下的时候,已知传输线等效电容 \(C_B = 200pF\),总线参考电压 \(V_{CC} = 3.3V\) 参数,通过如下步骤就可以计算出上拉电阻的阻值:

\[ \begin{cases} R_{P_{max}} = \frac{t_R}{0.8473 \times C_B} = \frac{300 \times 10^{-9}}{0.8473 \times 200 \times 10^{-12}} = 1.77 kΩ \\ R_{P_{min}} = \frac{V_{CC} - V_{OL_{max}}}{I_{OL}} = \frac{3.3 - 0.4}{3 \times 10^{-3}} = 966.667 Ω \end{cases} \]

注意:上述计算步骤采用了前面 I2C 总线规范参数表格当中的数据,

经过上述的计算步骤,就可以基于当前的速率与功耗需求,选择

966.667Ω ~ 1.77kΩ 范围之间的任意上拉电阻值。

内置集成电路总线协议 I²C 简明指南