基于 Polar Si9000e 计算传输线特征阻抗的全攻略

伴随近几年集成电路制程工艺的进步,PCB

传输线上信号的频率逐年提高,非常容易导致信号在传输过程当中,由于受到传输线的阻力而出现插损(插入损耗,单位为分贝),这种信号在传输过程中受到的阻力被称为特性阻抗或者特征阻抗。换而言之,如果信号在传输过程当中,传输路径上的特征阻抗发生了变化,信号就会在阻抗不连续的结点发生反射。因而

PCB

上的传输线仅仅只解决通和断的问题还远远不够,还需要进一步确保其传输链路上特性阻抗的匹配和连续。

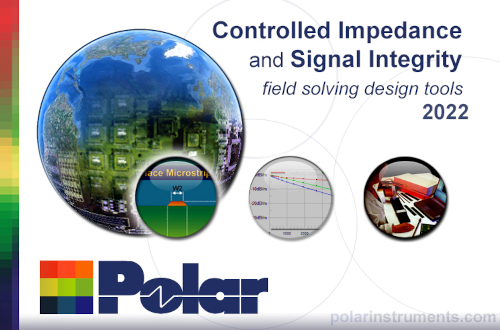

英国宝拉 POLAR

公司推出的 Si9000e,正是一款这样可以预测

PCB

走线阻抗的计算工具,该工具已经成为高速电路设计当中,必不可少的辅助工具。该工具提取了

100 余种 PCB

传输线的典型结构,并且基于这些结构对指定频率下的传输线阻抗进行建模计算。Si9000e

将影响 PCB

传输线阻抗的主要因素:板材厚度、顶层走线宽度、铜泊厚度、走线周围的包地间距、表面绿油的厚度

作为输入参数,就可以计算出表面单端/差分和共面单端/差分类型走线的阻抗。

英文词汇准备

由于 Si9000e 传输线场求解器(Si9000e Transmission Line Field Solver)采用的是全英文界面,因而在开始正式的内容之前,需要将软件界面高频出现的专业英文词汇,整理在下面的表格当中:

| Si9000e 界面英文词汇 | Si9000e 界面英文词汇 |

|---|---|

| Stripline [ˈstrɪplaɪn] n.带状线,电介质条状线 | Coplanar [kəʊˈpleɪnə(r)] adj.共面的 |

| Microstrip [ˈmaɪkrəʊstrɪp] n.微带线,微波传输带 | Coated [ˈkəʊtɪd] adj. 覆盖有阻焊油墨的 |

| Waveguide [ˈweɪvˌɡaɪd] n.波导 | Coarse [kɔːs] adj. 粗略的 |

| Substrate [ˈsʌbstreɪt] n.基层 | Single-End [ˈsɪŋɡl end] adj.单端的 |

| Dielectric [ˌdaɪɪˈlektrɪk] n.电介质 | Differential [ˌdɪfəˈrenʃ(ə)l] adj.差分的 |

| Thickness [ˈθɪknəs] n.厚度 | Separation [ˌsepəˈreɪʃn] n.隔离 |

| Cutout [ˈkʌtaʊt] n.分割 | Lossless [ˈlɒsləs] adj.无损的 |

| Tolerance [ˈtɒlərəns] n.公差 | Trace [treɪs] n. PCB 上的铜质走线 |

注意:本文后续内容会将 Si9000e 直接简写为 Si9000。

微带线 & 带状线

PCB 电路网络当中的信号走线,可以划分为 微带线(Microstrip)和 带状线(Stripline)两种主要类型:

- 微带线(Microstrip):即 PCB 表面的带状走线,由于一面裸露在空气中,可以向周围形成辐射或受到周围的辐射干扰,而另一面附着在 PCB 绝缘电介质上,所以其形成的电场一部分分布在空气中,另一部分分布在 PCB 的绝缘介质里,其信号传输速率高于带状线。

- 带状线(Stripline):即 PCB

内层的带状走线,由于嵌在两层导体之间,所以其电场分布在两层导体所形成的平面之间,能量不会被辐射出去,也不会受到外部辐射的干扰。由于其周围分布的是介电常数大于

1的电介质,所以信号传输速率要慢于微带线。

无论是微带线还是带状线,在 PCB

当中这些走线的单位通常会采用密尔

mil,其与公制毫米 mm

的换算关系如下面等式所示:

1 | 1 密耳(mil) = 0.0254 毫米(mm) |

共面单端 & 共面波导

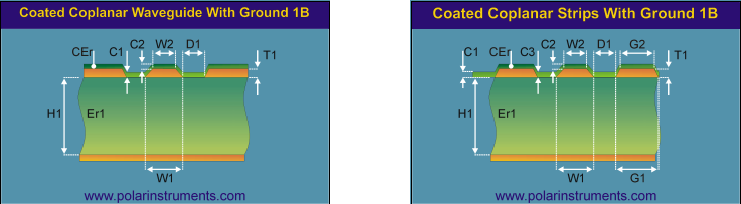

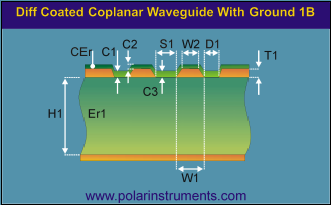

传输线理论当中的共面波导(下图左)与共面单端(下图右)两种走线模型,是非常容易混淆的两个概念:

- 共面波导(CPW,Coplanar Waveguide)是指在介质平面上制作出中心导体带,并在紧邻中心导体带的两侧制作出导体平面,这样就构成了共面波导,其本质上属于一种共面微带传输线(上图左)。

- 共面单端(Coplanar Single-Ended)走线的概念类似于共面波导,不同之处在于其中心导体带两侧是指定宽度的接地走线,而非一个完整的地平面(上图右)。

注意:当采用 Si9000 计算阻抗的时候,由于共面单端需要输入的计算参数更多。因此,在没有特别严格要求的情况下,可以直接使用共面波导作为阻抗计算的模型,同样参数情况下两者的计算结果差异非常细微。

常用 PCB 叠层结构

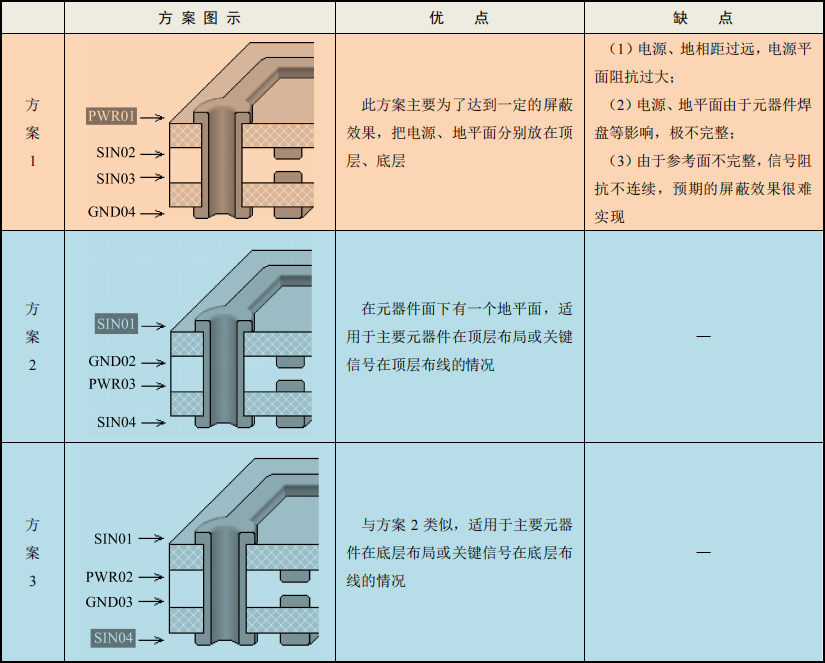

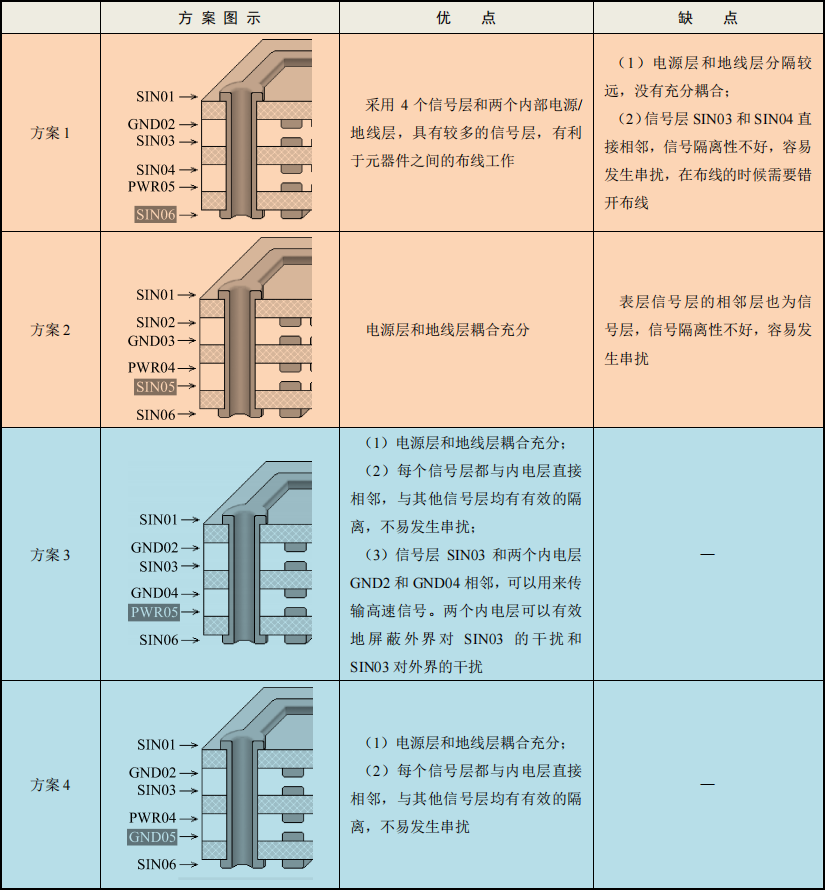

实际的 PCB 设计工作当中,在完成元件的布局摆放之后,会首先对 PCB

布线的瓶颈位置进行分析,根据敏感信号线的种类和数量来确定信号层的层数。然后再根据电源的性能参数要求,来确定内电层的层数。从而最终确定整个

PCB 的叠层设计方案。下面的表格对比了 3 种常见

四层 PCB 叠层方案 的优缺点(通常会优先选择第

2 和第 3 号叠层方案):

而在接下来的表格里,则是对比了 4 种常见 六层 PCB

叠层方案 的优缺点(通常会优先选择第 3 和第

4 号叠层方案):

Si9000 主界面介绍

Si9000 软件的主界面可以被划分为【功能选择标签】、【模型选择区域】、【参数输入与计算区域】、【单位切换区域】四个区域:

- 【功能选择标签】:在计算 PCB 特征阻抗的时候,需要将切换至无损计算(Lossless Calculation)标签。

- 【模型选择区域】主要用于选择 PCB 典型层叠结构与走线方式的特征阻抗模型。

- 【单位切换区域】用于在

米尔(

Mils)、英寸(Inches)、微米(Microns)、毫米(Millimetres)计算单位之间进行切换。 - 【参数输入与计算区域】用于输入 PCB 各种基材、铜层、阻焊油墨、走线的参数信息,并且利用这些信息计算出相应的特征阻抗。

注意:勾选软件底部的【Auto Calc】可以开启自动计算功能,即当参数输入区域发生变化的时候,Si9000 就会自动计算出对应的特征阻抗结果。

常见的阻抗模型

现代传输线理论认为,信号在传输过程当中,特征阻抗的不连续会造成反射现象。而在信号完整性领域,反射、串扰、参考平面分割

都会导致阻抗的不连续问题,因而传输线特征阻抗的匹配显得尤为重要。在下面的列表里,对高速电路设计当中存在的一些概念进行了解释:

- 时延:高速信号从电路网络的一端传送至另一端所需的时间。

- 串扰:信号线之间的互感与互容所引发的噪声。

- 反射:在传输线上阻抗不连续的位置,一部分信号会继续向前传输,另外一部分则会被反射形成回波。

- 振铃:由于传输线的阻抗不匹配,导致信号被多次反射叠加之后,所出现的振荡波形。

常见的阻抗计算模型可以划分为内层或者外层的

单端、差分、共面单端、共面波导、差分共面地、差分共面波导

一共 12 种模型:

| 外层单端 | 内层单端 |

|---|---|

|

|

| 外层差分 | 内层差分 |

|

|

| 外层共面单端 | 内层共面单端 |

|

|

| 外层共面波导 | 内层共面波导 |

|

|

| 外层差分共面地 | 内层差分共面地 |

|

|

| 外层差分共面波导 | 内层差分共面波导 |

|

|

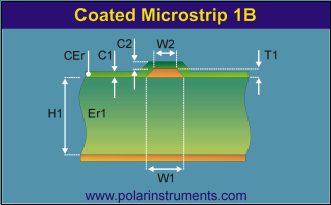

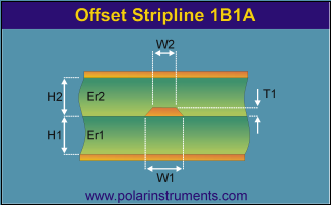

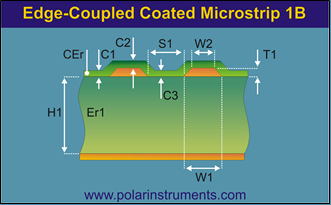

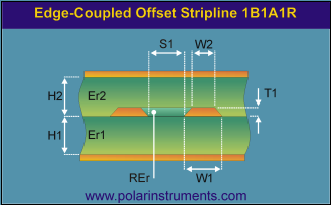

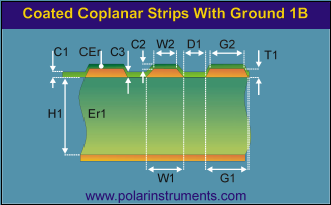

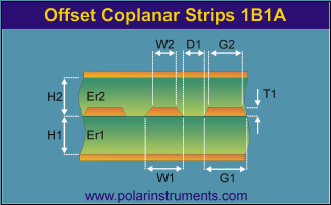

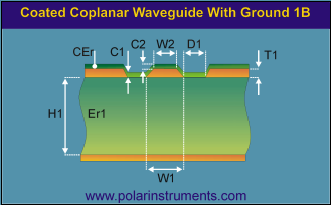

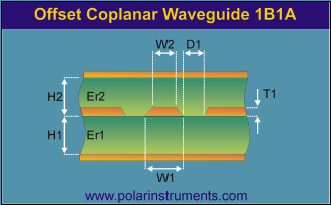

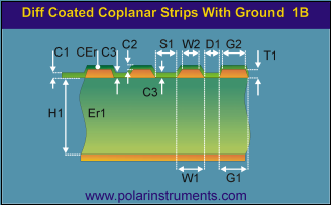

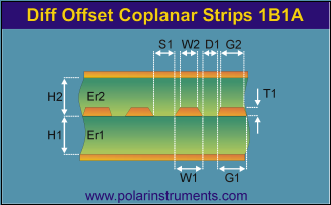

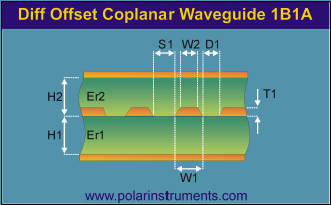

影响上述模型当中特征阻抗的因素有基材厚度、介电常数、铜层厚度、线宽、线距、阻焊油墨厚度等,具体请参考下面的表格:

| 缩写 | 英文名称 | 功能描述 |

|---|---|---|

| H1 | Substrate 1 Height |

第 1 层基材的厚度(不包含铜厚); |

| H2 | Substrate 2 Height |

第 2 层基材的厚度(不包含铜厚); |

| Er1 | Substrate 1 Dielectric |

第 1 层基材的介电常数(多种基材压合时取平均值); |

| Er2 | Substrate 2 Dielectric |

第 2 层基材的介电常数(多种基材压合时取平均值); |

| W1 | Lower Trace Width |

阻抗走线的下线宽; |

| W2 | Upper Trace Width |

阻抗走线的上线宽; |

| G1 | Lower Ground Strip Width |

接地走线的上线宽。 |

| G2 | Upper Ground Strip Width |

接地走线的下线宽。 |

| D1 | Ground Strip Separation |

接地走线的间隔距离; |

| T1 | Trace Thickness |

走线的铜层厚度; |

| C1 | Coating Above Substrate |

基材的阻焊油墨厚度; |

| C2 | Coating Above Trace |

铜皮或者走线的阻焊油墨厚度; |

| C3 | Coating Between Traces |

铜层走线间隙的阻焊油墨厚度; |

| CEr | Coating Dielectric |

阻焊油墨的介电常数; |

注意:残铜率是指板 PCB 上面

覆铜面积与整板面积之比,例如未经加工的覆铜芯板的残铜率为100%,而将表面铜层全部被蚀刻掉之后残铜率就变为0%。

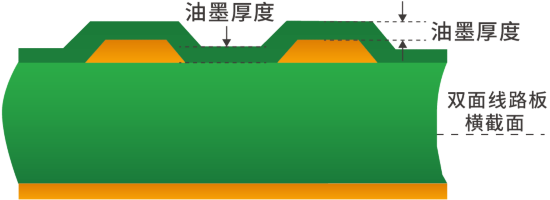

导线的上/下线宽换算关系

目前的 PCB 蚀刻制造工艺,会导致铜层走线出现上窄下宽的情况,形成类似下图这样的梯形截面走线:

接下来的表格展现了不同基础铜厚情况下,铜层走线的 \(W_{上/下线宽}\) 以及 \(D_{线距}\),与 \(W_{设计线宽}\) 和 \(D_{设计线距}\)

之间的换算关系(如果不需要精确的计算,那么可以默认 \(W_{上线宽}\) 比 \(W_{下线宽}\) 要窄约

1mil,具体参数建议咨询 PCB 生产厂家):

| 基础铜厚 | 上线宽 \(W_{上线宽}\) | 下线宽 \(W_{下线宽}\) | 线距 \(D_{线距}\) |

|---|---|---|---|

| 18μm(内层) | \(W_{设计线宽} - 0.1 mil\) | \(W_{设计线宽}\) | \(D_{设计线距}\) |

| 35μm(内层) | \(W_{设计线宽} - 0.4 mil\) | \(W_{设计线宽}\) | \(D_{设计线距}\) |

| 70μm(内层) | \(W_{设计线宽} - 1.2 mil\) | \(W_{设计线宽}\) | \(D_{设计线距}\) |

| 42μm(负片层) | \(W_{设计线宽} - 0.4 mil\) | \(W_{设计线宽} + 0.4 mil\) | \(D_{设计线距} - 0.4 mil\) |

| 48μm(负片层) | \(W_{设计线宽} - 0.5 mil\) | \(W_{设计线宽} + 0.5 mil\) | \(D_{设计线距} - 0.5 mil\) |

| 65μm(负片层) | \(W_{设计线宽} - 0.8 mil\) | \(W_{设计线宽} + 0.8 mil\) | \(D_{设计线距} - 0.8 mil\) |

| 12μm(外层) | \(W_{设计线宽} - 0.6 mil\) | \(W_{设计线宽} + 0.6 mil\) | \(D_{设计线距} - 0.6 mil\) |

| 18μm(外层) | \(W_{设计线宽} - 0.6 mil\) | \(W_{设计线宽} + 0.7 mil\) | \(D_{设计线距} - 0.7 mil\) |

| 35μm(外层) | \(W_{设计线宽} - 0.9 mil\) | \(W_{设计线宽} + 0.9 mil\) | \(D_{设计线距} - 0.9 mil\) |

| 12μm(镀金工艺外层) | \(W_{设计线宽} - 1.2 mil\) | \(W_{设计线宽}\) | \(D_{设计线距}\) |

| 18μm(镀金工艺外层) | \(W_{设计线宽} - 1.2 mil\) | \(W_{设计线宽}\) | \(D_{设计线距}\) |

| 35μm(镀金工艺外层) | \(W_{设计线宽} - 2.0 mil\) | \(W_{设计线宽}\) | \(D_{设计线距}\) |

注意:信号层主要用于走线,通常采用正片方式处理;而电源层和接地层通常采用负片方式处理,这样只需指定无需铺铜的位置即可,可以较大程度降低 EDA 工具的数据处理量。

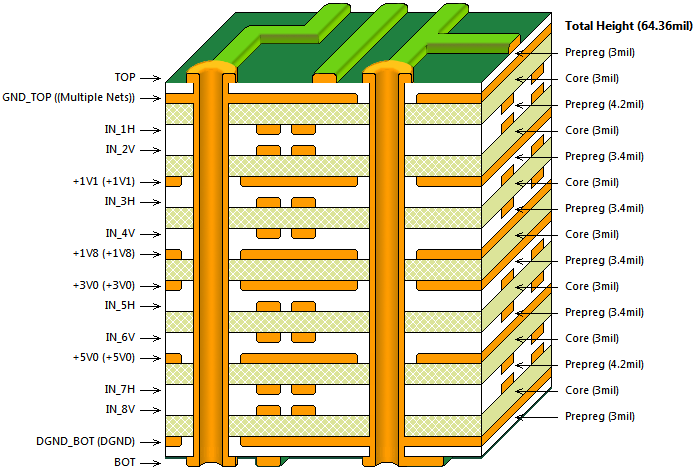

芯板与半固化片

多层 PCB 都是由 FR-4 材料的

覆铜芯板(Core)与具有粘结功能的

半固化片(PP,Prepreg [priːpreɡ])热压合而成,当使用

Si9000 计算带有叠层结构的 PCB

特性阻抗时,纳入计算的板材厚度应当由两者共同叠加而成,下图清晰的展示了覆铜芯板与半固化片之间的这种叠加关系:

芯板的介电常数

普通 FR-4 材料的 覆铜芯板(Core),主要有南亚、建滔、生益、宏瑞等板材生产厂家,下面两个表格展示了Tg ≤ 170 型与 IT180A S1000-2 型的 生益 FR-4 芯板,在各种厚度下所对应的介电常数:

| 生益 FR-4 芯板厚度 | 0.051mm/2mil | 0.075mm/3.0mil | 0.102mm/4mil | 0.11mm/4.33mil | 0.13mm/5.1mil | 0.15mm/5.9mil | 0.18mm/7.0mil |

|---|---|---|---|---|---|---|---|

| Tg ≤ 170 型 | 3.6 | 3.65 | 3.95 | 无此规格 | 3.95 | 3.65 | 4.2 |

| IT180A S1000-2 型 | 3.9 | 3.95 | 4.25 | 4 | 4.25 | 4.25 | 4.5 |

| 生益 FR-4 芯板厚度 | 0.21mm/8.27mil | 0.25mm/10mil | 0.36mm/14.5mil | 0.51mm/20mil | 0.71mm/28mil | ≥0.8mm/≥31.5mil |

|---|---|---|---|---|---|---|

| Tg ≤ 170 型 | 3.95 | 3.95 | 4.2 | 4.1 | 4.2 | 4.2 |

| IT180A S1000-2 型 | 4.25 | 4.25 | 4.5 | 4.4 | 4.5 | 4.5 |

半固化片的介电常数

半固化片(PP)比较有名的厂家是罗杰斯(Rogers),主要有

106、1080、3313、2116、7628

等规格,下面的这个表格展示了 Tg ≤ 170 型与

IT180A S1000-2

型半固化片,在各种规格下所对应的介电常数:

| Tg≤170 半固化片规格 | 106 | 1080 | 3313 | 2116 | 7628 |

|---|---|---|---|---|---|

| 理论厚度 (mm) | 0.0513 | 0.0773 | 0.1034 | 0.1185 | 0.1951 |

| 介电常数 | 3.6 | 3.65 | 3.85 | 3.95 | 4.2 |

| IT180A S1000-2B 半固化片规格 | 106 | 1080 | 3313 | 2116 | 7628 |

| 理论厚度 (mm) | 0.0511 | 0.07727 | 0.0987 | 0.1174 | 0.1933 |

| 介电常数 | 3.9 | 3.95 | 4.15 | 4.25 | 4.5 |

Si9000 阻抗计算实例

在高速电路设计过程当中,通常情况下

DDR、eMMC、SDIO

等单端信号会要求 50Ω 阻抗(可以将其设置为 EDA

工具走线的默认线宽)。而 HDMI、DDR

时钟 等差分信号则会要求 100Ω 阻抗,除此之外

USB 差分线则会要求 90Ω 阻抗。

为了匹配这些各不相同的特征阻抗需求,需要基于 Si9000 对走线的各种参数进行计算,从而获得合理的走线宽度与距离。由于使用 Si9000 进行无损计算的时候,所采用的参数与 PCB 生产厂家所使用的材料以及工艺密切相关,因而必须遵循厂家提供的相关参数,确保阻抗计算结果的准确性。这里的表格,展示的是某工厂最新使用的半固化片规格与其介电常数:

| 半固化片规格 | 7628 | 2216 | 3313 |

|---|---|---|---|

| 介电常数 | 4.4 |

4.16 |

4.1 |

而接下来的表格,则展示了该工厂所使用阻焊油墨的厚度以及介电常数:

| 基材上的油墨厚度 | 导线上的油墨厚度 | 阻焊油墨介电常数 |

|---|---|---|

0.8mil |

0.5mil |

3.8 |

注意:盎司

oz原本是一个用于表示重量的单位1oz = 28.350g,在 PCB 设计当中通常将其用于描述铜层的厚度,1OZ铜层对应的厚度约为0.035mm。

四层层叠方案 JLC04161H-7628

以某 PCB 生产厂家所提供的 JLC04161H-7628 型四层 PCB

叠层方案为例(PCB 成品厚度 1.59mm,内层铜厚

0.5oz,外层铜厚 1oz):

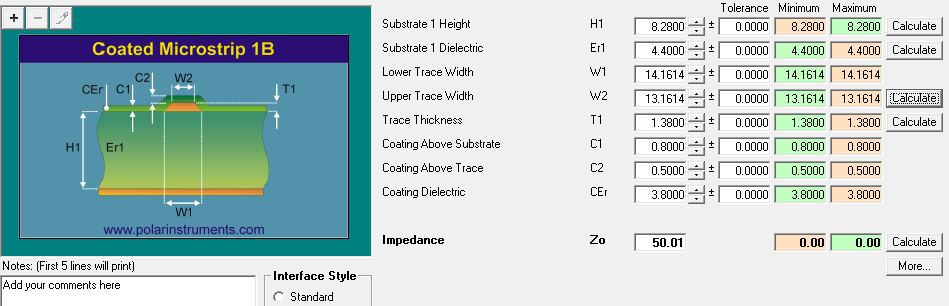

下图是使用 Si9000 计算 50Ω

欧姆外层单端阻抗走线的结果(即上下线宽度分别为

14.1614/13.1614mil 或者

0.35970/0.33430mm):

四层层叠方案 JLC04161H-3313

以某 PCB 生产厂家所提供的 JLC04161H-3313 型四层 PCB

叠层方案为例(PCB 成品厚度 1.56mm,内层铜厚

0.5oz,外层铜厚 1oz):

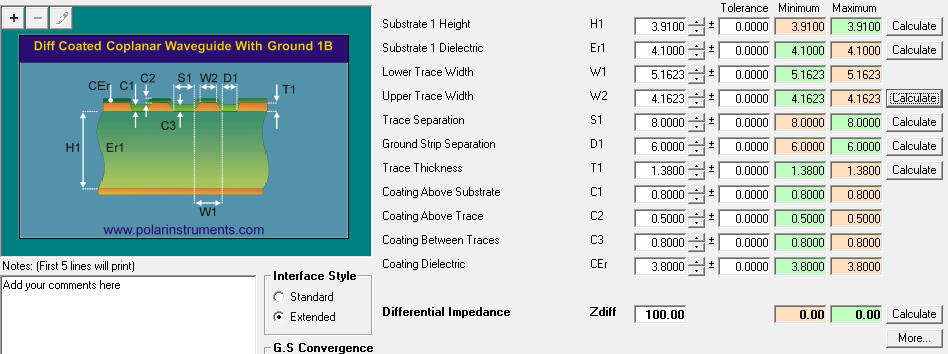

下图是使用 Si9000 计算 100Ω

欧姆外层差分共面阻抗走线的结果(即上下线宽度分别为

5.1623/4.1623mil 或者

0.13112/0.10572mm):

六层层叠方案 JLC06161H-3313

以某 PCB 生产厂家所提供的 JLC06161H-3313 型六层 PCB

叠层方案为例(上下线宽度分别为 1.6mm,内层铜厚

0.5oz,外层铜厚 1oz):

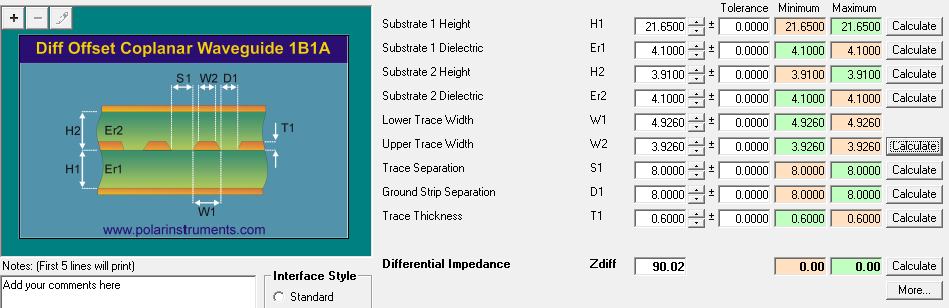

下图是使用 Si9000 计算 90Ω

欧姆内层差分共面阻抗走线的结果(即上下线宽度分别为

4.9260/3.9260mil 或者

0.12512/0.09972mm):

基于 Polar Si9000e 计算传输线特征阻抗的全攻略